## INTEGRATED CIRCUIT NEWS

国家"芯火" 双创基地 (平台)

国家集成电路设计杭州产业化基地 | 孵化器

浙江省集成电路设计与测试产业创新服务综合体

浙江省集成电路设计公共技术平台

# 杭州国家芯火双创基地

National Xinhuo Platform of Hangzhou for Innovation and Entrepreneurship

## 引频而发展

## 助分試腦飞

杭州国家"芯火""双创基地(平台)是由国家工信部于2018年3月批复,依托杭州国家集成电路设计产业化基地建设的国家"芯火"平台。平台以产业共性需求为牵引,以公共技术服务为核心,充分整合产业链资源,推动形成"芯片-软件-整机-系统-信息服务"的生态体系,着力提升区域集成电路产业的核心竞争力,推进我国集成电路核心关键技术的自主创新,引导电子信息产业向价值链高端发展。

## 1 平台服务

## 公共技术平台

由EDA云平台、流片服务子平 台、封装测应用解决方案子平 台等组成。应用解决方案子平 台等组成。 3

## 咨询服务平台

与浙江省半导体行业协会密切 协同,为地方各级政府和企业 提供行业咨询、信息共享等服 冬

**(**)

## 芯机联动平台

围绕集成电路上下游产业链,推动集成电路企业与系统整机企业供需对接,深化"政产学研用金"高效联动。

## 人才培训平台

协同企业、高校、科研院所等 优势资源 开展多层次人才培训、 实训,多维度培养集成电路复合

服务体系

## 企业孵化平台

以"孵小、扶强、引外"为宗旨,搭建孵化空间,聚焦企业痛点、难点,提供专业精准服务。

#### EDA

提供Siemens EDA, Cadence 和行芯科技等公司的EDA软 件服务。

, 01

## 流片

提供台积电、中芯国际、华虹宏力、华润上华、 Foundries等流片一站式服

, UZ

## 封 测

提供集成电路测试程序开发、 晶圆测试、成品测试、失效 分析、芯片封装等服务。

<sub>≈</sub> U.5

#### - 1

IP设计.验证、测试和 集成服务,支持企业进行 产业化和应用。

. 04

公共技术服务

## 2 平台资质

## 国家集成电路设计杭州产业化基地

National Integrated Circuit Design Industrialization Base (Hangzhou)

中华人民共和国科学技术部

## 浙江省中小企业公共服务示范平台

Zhejiang Public Service Platform for Small and Medium-sized Enterprises

浙江省经济和信息化厅

## 浙江省集成电路设计公共技术平台

浙江省科学技术厅

#### 浙江省集成电路产业技术联盟 常务副理事长单位

Zhejiang Integrated Circuit Industry Technology / Executive Vice President Corporation

#### 国家集成电路人才培养基地 杭州培训中心

中华人民共和国教育部 中华人民共和国科学技术部

#### 面向半导体芯片领域的产业技术 基础公共服务平台

Public Service Platform for Semiconduc Industry Technology 中华人民共和国工业和信息化器

#### 浙江省集成电路设计与测试 产业创新服务综合体 Zhejiang Integrated Circuit Design and Testin

-1 10

## 杭州国家芯火双创基地(平台)

National Xinhuo Platform for Innovation as Entrepreneurship(Hangzhou) 中华人民共和国工业和信息化部

## 目录 **CONTENTS** ▲中国数谷·"滨创汇"集成电路产业创新沙龙在高新区(滨江)举办 ▲2025 年度浙江省集成电路专业高级职称申报解析活动成功举办 ▲悉智科技: 宽禁带功率模组生产基地签约杭州城东智造大走廊 **-** 05 ▲浙江萃锦: 年产 120 万只中高功率半导体器件项目开工 ▲安诺逻辑: 半导体封测中心建设项目举行开工仪式 - 07 ▲浙大余杭量子研究院:全国首台国产商业电子束光刻机面世 ▲广立微:战略并购 Luceda,剑指硅光市场 ▲全芯微:首台 12 英寸前道 ArF 匀胶显影设备(Track)顺利交付 ▲云豹智能: AI 网络研发中心总部项目入驻"中国视谷"的芯机社区 ▲总投资超50亿元,杭绍临空示范区9个项目集中签约 ▲晶能微电子:车规级 SiC 模块连续多月交付量超万套,上车极氪全系产品 △江丰电子: 拟与爱发科筹划整合双方平板显示靶材业务 ▲2025 上半年浙江 "415X" 先进制造业集群规上营收创新高 • 芯资讯 ▲Q2 全球 TOP20 芯片公司榜单 ▲工信部:集成电路(上半年)产量+8.7%、出口+20.6%、设计+18.8% ▲中国 FlipFET 技术颠覆芯片 ▲中科院微电子所在芯粒集成电迁移 EDA 工具研究方向取得重要进展 ▲垂直氮化镓重磅发<u>布</u> ▲九峰山实验室首发 6 英寸 InP 激光器与探测器外延工艺 △中国算力规模全球第二,AI 专利数占全球六成 ▲光罩技术的较量 △英伟达披露 CPO 路线图 ▲PCIe 8.0 正式发布,有望实现 256GT/s 的 AI 性能 ▲全国各地集成电路扶持政策 • 芯政策 ▲浙江省委办公厅省政府办公厅印发《关于全面推进科技创新和产业创新深度融合的实施 ▲浙江省科学技术厅关于组织申报 2026 年度省 "尖兵" 领雁"科技计划科技合作项目的 ▲杭州市上城区人民政府办公室关于印发《上城区支持人工智能产业创新发展若干政策措 芯观点 ▲中国工程院院士倪光南:构建脑、眼、行动协同的系统,提高机器人智能水平 ▲清华大学汪玉教授:当 AI 重塑产业,新时代的育人思考 ▲如何做好人形机器人的"五官"与"皮肤"? 芯伙伴

0000

《天堂之芯》杂志转载的文章内容系作者个人观点,仅为传达不同的观点,不代表本杂志对该观点的态度。

## 中国数谷·"滨创汇"集成电路产业创新沙龙在高新区 (滨江)举办

8月26日下午,中国数谷·"滨创汇"集成电路产业创新沙龙在高新区(滨江)"中国数谷"大厦举办。区委副书记、管委会主任、区长郑迪,西湖大学副校长、欧洲科学院外籍院士仇旻,省有关部门负责人武文明、张志宁,市有关部门负责人吕明忠,区领导高翀等出席。

本次活动聚焦 EDA 串链、AI 和智能制造,以强化 区内创新要素精准对接、提升科技成果转化效率为议题, 深入研讨如何夯实创新要素供给体系,加快前沿技术向 产业动能转化的路径,为"创新滨江"的建设持续供能。

活动现场,浙江大学教授、杭州国家"芯火"双创基地(平台)总经理丁勇作《浙江省集成电路产业全景与杭州高新区(滨江)产业发展成效》主题分享。他指出,高新区(滨江)是杭州市集成电路发展的重要承载区,产业规模占全市集成电路的39.6%。目前,区内产业链布局完善,已实现设计、制造、封测等关键环节的

全覆盖,尤其在设计领域优势突出,汇聚了一批具有国际竞争力的龙头企业与创新型企业。近年来,高新区(滨江)产业生态持续优化,公共服务平台能级不断提升,产业集群效应加速显现,人才政策支持有力,高能级创新平台加快集聚,为高新区(滨江)集成电路产业提能升级奠定了坚实基础。

活动期间,中国工程院院士、浙江大学信息学部部长吴汉明,西湖大学副校长、欧洲科学院外籍院士仇旻,杭州广立微电子股份有限公司董事长郑勇军分别作了主题分享。

现场举行了《2025 浙江省 EDA 产业白皮书》发布仪式、EDA 创新联合体签约仪式、

同期,活动还举办了集成电路产业链创新闭门会,邀请重点企业围绕"国产 EDA 串链""AI+智能制造"两大主题展开深度交流,凝聚发展共识。

在政策解读环节,浙江省半导体行业协会产业协同中心王安宁就 2025 年度浙江省集成电路专业高级职称申报政策与申报流程进行解析,系统介绍了职称评审改革背景、申报条件、系统填报流程等重点内容,涵盖个人用户与用人单位的操作要点,帮助与会人员准确理解政策要求、掌握申报流程。

据了解,高新区(滨江)集成电路产业起步较早,是国家最早批准的7个国家集成电路设计产业化基地之一。多年来,高新区(滨江)坚持以做强芯片设计和制造为核心,延伸布局半导体材料、装备制造、封装测试、EDA软件等上下游环节,持续迭代集成电路专项政策,大力推动强链延链补链,形成了较为完善的"芯片一软件一整机一系统一信息服务"产业生态。目前,拥有士兰微、矽力杰、长川科技、中吴芯英等一批行业龙头企业,集聚了超150家集成电路产业链上下游企业;其中,设计企业超120家,涵盖AI芯片、功率芯片、汽车芯片和存储芯片等多个核心品类。上半年,全区集成电路产业集群营收180.2亿元,增长14%,规模保持全省第一。

"滨创汇"作为滨江产业创新品牌,未来将持续聚 焦集成电路、数据要素等重点领域,打造多形式、多层 次的生态共创平台,为"创新滨江"建设注入澎湃动力, 助力区域集成电路产业迈向全球创新高地。

本次活动由浙江省半导体行业协会、杭州高新区(滨江)财政局指导,杭州高新科创集团有限公司主办,杭州市高新区(滨江)发展和改革局、杭州高新区(滨江)经济和信息化局、杭州高新区(滨江)人力资源和社会保障局、杭州国家集成电路设计产业化基地有限公司协办。

## 2025年度浙江省集成电路专业高级职称申报解析活动 成功举办

为助力 2025 年度浙江省集成电路专业高级职称审核工作顺利开展,2025 年 8 月 29 日,杭州国家"芯火"双创基地(平台)联合浙江省半导体行业协会在腾讯会议以网络直播的形式成功举办"2025 年度浙江省集成电路专业高级职称申报解析"活动,吸引了近百名集成电路企业的相关人员参加。

在活动中,讲解人员围绕申报政策的关键环节,从 政策内容、核查依据、系统填报以及常见问题等多个方 面进行了全面且深入的解读。通过生动形象、通俗易懂 的讲解方式,与会人员对集成电路专业高级职称评审的 全流程有了更为深入和清晰的认识,这不仅有效提升了 申报人的工作效率,更为集成电路企业的发展提供了坚 实有力的支持。

下一步,杭州国家"芯火"双创基地(平台)将联合浙江省半导体行业协会持续为集成电路产业的专业人才培养和企业发展提供全方位、多层次的支持与服务,助推浙江省集成电路产业发展。

#### >>> 常见问题解答

- 1.满足申报条件,但是评审条件业绩项不满足10选3可否申报? (可以)

- 2.继续教育平台专业课找不到集成电路专业? (选择"信息技术")

- 3.什么叫核心期刊或高质量期刊? (指由北京大学图书馆、南京大学图书馆和北京高校图书馆期刊工作研究会评定出版的《中文核心期刊目录总览》,或被SCI、EI检索的期刊。)

- 4.入职现单位还不满五年,年度考核怎么办? (找上一家任职单位补足)

- 5.单位审核首次公示5日后,进行修改是否需要重新公示? (不需要)

- 6.外省可否进行浙江省集成电路高级职称申报? (社保、档案起码有一项在省内)

- 7.自评分表是否一定要填写? (除了第九条业绩突出申报外,都需要填写上传)

- 8.受理点如何选择? (不要选浙江省半导体行业协会,选企业所属中评委)

#### >>> 常见问题解答

#### 9.申报方式如何勾选? (申报条件第七条)

- 具有本专业或相近专业博士学位,取得工程师职务任职资格后,实际聘任工程师职 62年以上。(正常申报)

- 2. 具有本专业或相近专业大学本科及以上毕业学历,取得**工程师任职资格**后,实际聘任工程师职务 5 年以上。(正常申报)

- 3. 取得高级技师(一级)职业资格或职业技能等级后实际从事集成电路专业技术工作 满4年。(核能人才申报)

### >>> 常见问题解答

#### 9.申报方式如何勾选?

- 4. 世界技能大赛银牌和铜牌获得者、全国技术能手、国家级技能大师工作室领办人、 钱江技能大奖获得者、浙江杰出工匠,省"百千万"高技能领军人才培养工程入选的"杰出技能人才"。(**破格申报**)

- 5. 取得数字技术工程师高级专业技术等级证书(集成电路专业)。(破格申报)

- 6. 按照《浙江省集成电路专业高级工程师职务任职资格量化赋分标准》,自评分达到65分以上。(自评分申报)

- 10.论文查重的平台、网站、查重率是否有要求? (平台和网站没有要求,查重率以最后专家评审判断为主)

核查联系方式: 赵燕明 0571-86726367

## 悉智科技: 宽禁带功率模组生产基地签约杭州城东智造 大走廊

8月21日上午,杭州城东智造大走廊临平片区迎来了一场备受瞩目的重大项目集中签约仪式。此次签约活动汇 聚了众多优质项目,为该片区的产业发展注入了新的强大动力。

在众多签约项目中,悉智科技宽禁带功率模组生产基地项目格外引人注目。据了解,该项目由苏州悉智科技有限公司投资建设,总投资规模约达 20 亿元。如此大规模的投资,彰显了企业对该项目的高度重视以及对杭州城东智造大走廊临平片区发展前景的充分信心。

苏州悉智科技有限公司是一家在行业内颇具影响力的高新技术企业。获悉,该公司专注于车规级宽禁带功率与电源模块的研发与生产,在相关领域拥有深厚的技术积累和丰富的实践经验。其产品在汽车、工业等多个领域具有广泛的应用前景。

此次签约的项目主要用于建设宽禁带模组生产基地。根据掌握的信息,基地将新建电驱产线、高端工业壳封塑封产线和汽车电源产线。这些先进的生产线将采用前沿的技术和设备,有助于提高生产效率和产品质量,进一步增强悉智科技在宽禁带功率模组领域的市场竞争力。

对于杭州城东智造大走廊临平片区而言,悉智科技项目的落地具有重要意义。有分析认为,该项目不仅将带来 大量的资金投入和就业机会,还将促进当地产业的升级和创新发展。随着项目的推进,有望吸引更多相关企业和人 才集聚,形成更加完善的产业生态。

悉智科技宽禁带功率模组生产基地项目的签约,是杭州城东智造大走廊临平片区产业发展的一个重要里程碑。 未来,双方将携手共进,充分发挥各自优势,推动项目早日建成投产,为区域经济的高质量发展贡献力量。我们也 期待悉智科技在这片土地上创造出更加辉煌的业绩。

(来源:今日半导体)

浙江萃锦:年产120万只中高功率半导体器件项目开工

8月5日消息,由中国电子系统工程第四建设有限公司(以下简称"中电四公司")承建的浙江萃锦半导体有限公司年产120万只中高功率半导体器件项目开工仪式,于当日在宁波慈溪市高新区盛大举行。现场气氛热烈,众多行业嘉宾、项目团队成员齐聚一堂,共同见证这一具有重要意义的时刻。

据了解,中电四公司在半导体工程建设领域拥有丰富的经验和卓越的技术实力。多年来,该公司参与了众多重大半导体项目的建设,凭借专业的团队和严格的质量管控体系,赢得了行业内的广泛认可。此次承接浙江萃锦半导体项目,中电四公司将充分发挥自身优势,确保项目顺利推进。

浙江萃锦半导体有限公司年产 120 万只中高功率半导体器件项目的正式开工,标志着项目全面进入建设阶段。 该项目规划科学合理,涵盖了先进的生产设备和完善的配套设施。在建设过程中,将采用一系列先进的技术和工艺, 以确保项目的高效建设和高质量完成。

中高功率半导体器件在现代电子信息产业中具有至关重要的地位,广泛应用于新能源、工业控制、通信等多个领域。然而,目前国内中高功率半导体器件的规模化生产能力仍有待提升。该项目建成后,将显著提高国内中高功率半导体器件的产量,满足市场对中高功率半导体器件日益增长的需求。

从产业发展的角度来看,该项目的建设对于增强我国半导体产业链供应链的韧性与安全具有重要意义。它将进一步完善我国半导体产业的布局,减少对国外相关产品的依赖,提升我国半导体产业的整体竞争力。同时,项目的实施也将带动上下游产业的协同发展,创造更多的就业机会和经济效益。

获悉,项目团队已经制定了详细的建设计划和时间表,将严格按照计划推进项目建设。预计在各方的共同努力下, 该项目将按时完工并投入使用,为我国半导体产业的发展注入新的动力。

(来源:今日半导体)

## 安诺逻辑: 半导体封测中心建设项目举行开工仪式

8月16日上午,备受瞩目的浙江安诺逻辑科技有限公司半导体封测中心建设项目正式举行开工仪式。这一项目的启动,不仅是浙江安诺逻辑科技有限公司发展历程中的重要里程碑,也为当地半导体产业的发展注入了新的活力。

该项目选址于新埭镇创新路 288 号。占地面积达 33.6 亩,总建筑面积约 4.8 万平方米。优越的地理位置

和充足的建设空间,为项目的顺利推进和未来的发展提供了坚实的基础。

从相关渠道了解到,此项目是浙江安诺逻辑科技有限公司在现有产品和核心技术的基础上进行的产业升级之举。公司将投资购买先进的生产设备,着力打造全新的自动化生产线。通过完善芯片封装技术,旨在实现具有高技术附加值半导体产品的封装产能建设,进一步提升公司在半导体领域的核心竞争力。

按照规划,项目建成后将形成年产 100 亿颗芯片的强大生产能力。这一规模的产能提升,将使浙江安诺逻辑科技有限公司在半导体市场中占据更有利的地位,满足不断增长的市场需求。

预计在今年年底之前,浙江安诺逻辑科技有限公司 将实现升规,产值突破亿元。这不仅体现了企业对自身 发展的信心,也展示了其在半导体产业领域的巨大潜力。

(来源:今日半导体)

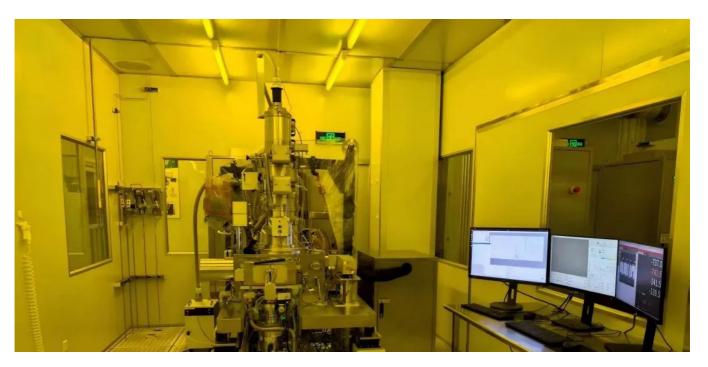

## 浙大余杭量子研究院:全国首台国产商业电子束光刻机 面世

近日,被誉为"纳米神笔"的国产电子束光刻机在杭州余杭正式亮相。这台设备由浙大余杭量子研究院自主研发,型号为"羲之",已完成研发并进入应用测试阶段,标志着我国在高端芯片研发核心装备领域取得重大突破。

据介绍,作为基地首批签约孵化项目,"羲之"是一款新一代 100kV 电子束光刻机,模样酷似大型钢柜,电子显示屏上不断闪烁着实时参数,专注于量子芯片和新型半导体器件的前沿工艺开发。它无需掩模版,通过高能电子束直接在硅片表面"手写"电路,精度可达 0.6nm、线宽仅 8nm,可多次修改设计,大幅提高研发效率。

据研发团队负责人表示,"这不仅是一台设备,更像一支能在头发丝上雕刻整座城市地图的纳米画笔。"与传统光刻机相比,电子束光刻机在原型设计、快速迭代和小批量试制方面具有独特优势。"芯片研发初期会设计很多版型、图案,常常需要一条线一条线进行修改,电子束光刻机精度高、'书写'便捷,极大提升了芯片研发初期反复调试的效率。"

"羲之"的命名源自中国古代书法大家王羲之,寓意用电子束代替毛笔,在芯片上"写字作画"。其性能已比 肩国际主流水平,为国内量子芯片等高端器件的研发提供了自主可控的"刻刀"。

此前,先进电子束光刻机类设备受国际出口管制,国内顶尖科研机构和企业长期无法采购,"羲之"的落地彻底打破这一困局,目前已与国内企业及多家科研机构展开接洽。

(来源: 爱集微)

## 广立微:战略并购Luceda,剑指硅光市场

2025 年 8 月 12 日,广立微正式宣布透过旗下全资子公司 SMTX TECHNOLOGIES SINGAPORE PTE. LTD(广立微电子(新加坡)有限公司)以 4000 万欧元的价格收购比利时全球光电子设计自动化(PDA)先锋 LUCEDA 的 100% 的股权。

广立微与 Luceda)的结合,是集成电路与光子芯片两大技术脉络的深度交融,将会以更完整的解决方案、更卓越的技术实力,携手产业链伙伴,共同驾驭数字洪流,点亮通往智能未来的"光路"。

## LUCEDA 的产品、服务和价值

2014年,比利时微电子研究中心(IMEC)、根特大学(Ghent University)和布鲁塞尔自由大学(Free University of Brussels)的资深光电子专家和信息通讯技术专家联合创办的光子集成电路(PIC)设计自动化(PDA)软件公司 Luceda Photonics,致力于为客户提供光子集成电路设计、仿真、工艺设计工具包(PDK)搭建及运维的全流程软件和服务,协助光电子芯片设计师享有像集成电路设计师一样的"首次即成功 First-time-right photonic IC design software"的设计体验。

Luceda Photonics 推出的光子集成电路设计自动化平台 Luceda IPKISS,旨在为光子集成电路设计行业提供与 硅集成电路设计领域相同便利的工具,IPKISS 为光子集成电路设计提供了完整的流程,其中包括预定义的布线、版 图和线路仿真算法。从本质上说,Luceda 的设计软件将光子集成电路设计流程的所有方面(包括器件设计、线路 设计和版图验证)自动化并集成到一个基于 Python 语言的工具中,从而实现光子集成电路设计 IP 的共享和重用。 同时 IPKISS 还包括 IP 管理模块以及专门针对阵列波导光栅(AWG)的设计模块。此外,IPKISS 还涵盖硅(Si)、 氮化硅(SiN)、铌酸锂(LNOI)、磷化铟(InP)和氧化铝(Al<sub>2</sub>O<sub>3</sub>)等各种材料平台。IPKISS 使设计师能够轻松 生成可直接制造的芯片设计,从而加速产品开发。这个工具有助于促进硅光技术在激光雷达领域中的应用和创新。

| 产品类型         | 核心功能                                                |

|--------------|-----------------------------------------------------|

| V4 = + 11 \n |                                                     |

| 光电子芯片设       | 硅光芯片器件和电路自动化设计软件,用户可以使用 Python 在 IPKISS 中实现光电子芯片设计、 |

| 计自动化软件       | 仿真、验证和优化的开发全流程,主要功能包括器件设计、线路设计、设计验证及流片准备            |

| IPKISS       |                                                     |

| 一键式阵列波       | 专门针对阵列波导光栅(AWG)的设计模块,为阵列波导光栅(AWG)提供从高层级规格到可制        |

| 导光栅(AWG)     | 造版图的集成化设计环境。该工具通过全设计阶段的专业技术支持与精准控制,实现以下功能:          |

| 设计仿真模块       | - AWG 高层级规格定义                                       |

|              | - AWG 物理结构合成                                        |

|              | - 仿真与验证                                             |

|              | - 通过 DRC 的版图生成                                      |

| IP 管理模块  | 能够快速实现光电子设计 IP 自动测试和验证自动化,可在各种条件下测试和验证光子 IP 构建模 |

|----------|-------------------------------------------------|

|          | 块,包括:                                           |

|          | - 版图测试 (GDSII, XML)                             |

|          | - 网表测试 ( 版图 vs. 网表,网表 vs. 网表 )                  |

|          | - S 参数测试 - 器件性能测试 (性能指标)                        |

|          | - 虚拟制造测试                                        |

| Circuit  | 利用先进的电路分析功能,评估真实工作条件下的电路性能、分析设计容差并预估良率,提供以      |

| Analyzer | 下分析方法:                                          |

|          | - 参数扫描分析(Tracer Analysis)                       |

|          | - 工艺角分析(Corner Analysis)                        |

|          | - 蒙特卡洛分析(Monte Carlo Analysis)                  |

|          | - 版图感知蒙特卡洛分析(Layout-aware Monte Carlo Analysis) |

| 合作接口     | 可与其他上下游软件一键连接,主要接口有:                            |

|          | - Link for Ansys Lumerical                      |

|          | - Link for Tidy3D                               |

|          | - Link for 3DS Simulia                          |

|          | - Link for Siemens EDA                          |

|          | - Link for Check Mate DRC                       |

|          | - OptiLUCEDA Cosim                              |

| 服务       | PDK 的软件实现、 PDK 开发以及设计流程优化                       |

|          |                                                 |

当前的封装技术必须迎接更高的性能要求,尤其是在高密度互连、热管理和信号完整性等方面,为满足这些要求, Luceda 已经开始考虑芯片和模组的封装设计工具包(ADK),以及芯片测试设计工具包(TDK)。

LUCEDA 的产品与解决方案已成功打入中国、美国、日本、德国等集成电路与光子技术重镇,广泛而活跃的全球用户提供了宝贵的市场反馈,驱动产品持续优化,更具普适性与竞争力。

## 广立微收购 Luceda 剑指硅光市场,打通硅光制造良率的"任督二脉"

1970年代,科学家就开始在硅基材料上研究光子学。在2000年左右,硅光子技术进入商业应用领域,华为、谷歌、英特尔等多家企业研发硅光芯片相关的产品,随后在数据中心和长距离通信等高端市场等领域得到应用,这些市场的需求相对有限,限制了硅光芯片的发展。外加彼时芯片制程的发展还暂未接近物理极限,人们热衷于通过缩小芯片制程来提升芯片的性能,而非通过硅光子技术提升芯片性能。这也导致了硅光子在此前的发展不及预期。

随着人工智能(AI)的发展对数据传输速度和带宽要求越来越高,光子集成电路近来引起了工业界的广泛关注。 与此同时,光子集成电路封装技术(CPO),即光子和电子芯片在单个封装基板上的异质集成,也日益受到高性能 计算(HPC)领域的关注。这是由于,硅光芯片正是一种能实现高效、快速、低成本处理和传输大量数据的技术。 此外,随着硅芯片制程逐渐趋于物理极限,"超越摩尔技术"的概念也随之被提出。由于光子芯片对工艺节点的要 求不如电子芯片那样严苛,降低了对先进制程的依赖。因此,硅光芯片在一定程度上缓解了当前芯片发展的瓶颈问题, 也成为了"超越摩尔定律"的关键技术。

硅光芯片并非取代传统的集成电路技术,而是在后摩尔时代,帮助集成电路扩充其性能。和微电子一样,硅光子芯片的生产制造也基于 CMOS 和 BiCMOS 等集成电路工艺线。因此充分利用微电子芯片生产线的闲置或淘汰产能,可直接将成熟的集成电路工艺直接应用于硅光芯片的超大规模生产制造,技术迁移成本较低,这也成为了硅光芯片得天独厚的优势。

硅光芯片迈向规模量产的征途上,制造良率是横亘的"天堑"。当前,由于受到硅基光波导的纳米级刻蚀精度控制要求极高、光电异质集成界面存在的显著光功率损耗等问题的限制,硅光芯片整体制造良率较传统集成电路存在明显差距。在产业生态方面,虽然全球范围内已有数家晶圆厂提供多项目晶圆(MPW)服务,但这些服务多局限于较落后工艺节点,且头部代工厂仍采取较为严格的技术封锁策略;此外设计厂商为追求差异化性能频繁提出的工艺定制需求,不仅导致代工厂研发成本呈指数级增长,更对产线稳定性、产品良率及长期可靠性带来挑战。

广立微是国内首家实现成品率提升全流程闭环的 EDA 与晶圆级电性测试设备提供商。公司围绕着集成电路良率提升技术现已形成了一系列测试芯片、DFM、DFT 设计 EDA 工具及集成电路大数据分析与管理等软件,成为国内 EDA 领军企业。

LUCEDA 是 PDA 软件领域的领军企业,致力于为客户提供光电子芯片设计、仿真、PDK 搭建及运维的全流程软件和服务,协助光电子芯片设计师享有像集成电路设计师一样的"首次即成功"的设计体验。

广立微与 LUCEDA 的结合,是硅集成电路与半导体激光芯片两大技术的集合,EDA 和 PDA 深度耦合为光电协同设计平台(EPDA),未来双方将携手开发硅光类测试芯片、DFM 工具及晶圆级检测设备,逐步覆盖硅光芯片设计、制造、测试、良率提升方向的系统性解决方案,致力构建 "设计-制造"闭环的协同优化平台,持续聚焦硅光芯片产业化进程中的核心痛点,突破从技术研发到规模化量产的关键良率瓶颈,为全球硅光芯片产业提供从设计到批量生产的全生命周期技术支持。

#### 公允的收购价格

根据公告,LUCEDA的 2024 财年营收分 380 万欧元,2025 财年营收为 420 万欧元。此次收购价格 4000 万欧元是营收的大约 10 倍,作为一家成长型公司来说,广立微的此次收购价格还是符合市场价值。目前国内初创 EDA公司的估值都远大于 4000 万欧元,这也是国内 EDA 收购案难的原因。

广立微通过收购 LUCEDA,在细分领域建立先发优势,在填补国产空白的同时有望成为全球硅光解决方案的重要参与者。据 Yole 预测,2024 年全球硅光市场规模达 14 亿美元,2031 年将增至 61 亿美元,年复合增长率 22.4%。庞大的市场必将给公司带来丰厚回报。

(来源: 芯思想)

## 全芯微:首台12英寸前道ArF匀胶显影设备(Track) 顺利交付

2025年8月19日,全芯微公司于客户现场成功 交付首台自主研发的 12 英寸前道 ArF 匀胶显影设备 (Track),该设备正式投入客户生产线,这标志着全 芯微公司在突破高端 IC 制程设备壁垒方面取得了重大 讲展。

匀胶显影设备是集成电路制造前道关键工艺设备之 一,其技术与性能直接关系到光刻工艺的精细度和良率。 长期以来, Track 设备市场被少数国际巨头所垄断, 该 设备国产化率不足3%,其国产化突破是我国集成电路 产业链自主可控的关键环节之一。

本次交付的 12 英寸 ArF 匀胶显影机系统突破了匀 胶显影设备的多项关键技术,其集成了匀胶、显影、对 中等模块化单元,通过机械手实现晶圆在各工艺模块间 的自动化传输,有效保障了生产流程的效率和稳定性。 设备配置的高精密陶瓷热盘单元和边缘曝光(WEE) 单元,具备良好的温度控制均匀性和工艺一致性。该机 型的成功开发,实现了公司在逻辑电路、存储芯片、 CMOS 射频电路、功率器件、驱动芯片和 OLED 等制造 领域的应用突破。

此次可转债的成功发行,为甬矽电子的发展注入了 新的动力。市场期待,公司能借助此次募集的资金,加 快多维异构先进封装技术的研发与产业化进程,不断提 升产品竞争力和市场份额。同时,也希望甬矽电子能在 先进封装领域持续深耕,为我国半导体产业的自主可控 发展贡献更多力量。

首台 ArF 匀胶显影设备的成功交付,为公司进一步 突破芯片先进制程奠定了基础。全芯微将继续聚焦超大 规模集成电路领域,推进技术研发与产品创新,为客户 提供高性能、高可靠性的工艺设备解决方案,助力行业 发展。

(来源:全芯微)

# 云豹智能: AI网络研发中心总部项目入驻"中国视谷"的芯机社区

过去两天,萧山密集落子: 芯模社区、芯创社区、 芯机社区三大人工智能产业社区亮相,人工智能发展实 施方案及重磅政策接踵而至,剑指具有国际竞争力的 AI 创新与产业生态。

今日(8月15日),云豹智能 AI 网络研发中心总部项目(下简称"云豹智能")便应声入驻"中国视谷"窗口园区的芯机社区,成为第一家实质性落户的 DPU 独角兽企业,为萧山人工智能产业发展注入了一剂"强心针"。

云豹智能作为国内专注于云计算和 DPU 的行业龙 头企业和独角兽企业,获得了腾讯、中兴聚源、深创投、 杭州国投等产业方及知名投资机构的青睐。其自主研发 的第一代 400G 速率的 DPU 芯片已经成为国内首颗最 高速率 DPU 芯片,市场前景十分广阔。

此次云豹智能落户湘湖,计划总投资 10 亿元,落地后研发团队规模达到 100 人,5 年内累计研发投入 4.5亿元人民币以上,投产后 5 年内营收达 30 亿元。

令人惊叹的是,从初次接触到签约落地仅用35天, 萧山以"日日新"的速度回应产业风口。不论是政策对 接、场地安排,还是各类审批手续,每一个环节都以最 快的速度推进,最终实现了云豹智能的"闪电式"落户。

当前,云豹智能 AI 网络研发中心总部所处的湘湖 板块,正是萧山投资百亿建设芯机社区的落子之处。这

里左拥钱塘江,右枕湘湖水,时代大道贯通南北,地理位置得天独厚。未来将建成超 200 万平方米 "产城人文"融合的高标准产业空间,发展势能蓄势待发。

"这是优势互补的强强联合。"据湘湖国家旅游度假区管委会相关负责人介绍:"云豹智能入驻云尖信息产业园,同一天'出生'的这两家企业分属人工智能生态产业链的上下游企业,云豹智能聚焦芯片研发,云尖信息紧跟智算集群硬件研发制造。通过引进合作紧密度高的产业链企业,很大程度上是帮助企业把生态朋友圈建起来,进而更好开展产业链协同发展。"

随着云豹智能的成功落户,萧山人工智能产业发展的步伐将进一步加快。未来,萧山将继续秉持开放创新的理念,加大招商引资力度,优化产业生态,推动人工智能与实体经济深度融合,为经济转型升级注入新的活力,向着打造全省 AI 赋能新型工业化应用场景第一区的目标大步迈进。

(来源:萧山发布)

## 总投资超50亿元,杭绍临空示范区9个项目集中签约

8月15日上午,柯桥区招商引资工作会议暨五大发展平台工作交流会在绍兴国际会展中心举行。现场共有44个招商项目参加集中签约,计划总投资240亿元,其中上台签约项目21个,场外签约项目23个,涵盖光电信息产业、医疗健康产业、人工智能产业、高端装备及智能制造产业、商贸文旅产业等多个领域。

其中,杭绍临空示范区 9 个项目签约,总投资超 50 亿元。

先进封装 TGV 玻璃基板项目签约,项目计划借助对 PVD 技术的掌握和创新,以及在 TGV 前沿技术落地的关键 环节方面的先发优势,打造国内领先的先进封装领域的玻璃基板生产制造基地。

2.5D 先进封装生产制造基地项目签约,项目围绕芯粒关键技术开展研发和落地,作为中国 Chiplet 标准的发起方,参与行业标准制定并致力于提供国产化设计和工艺全流程封装平台。

此外,AloT 智能设备总部及生产中心项目公司拟将总部搬迁至柯桥,并投资建设智能物联设备制造中心,主要生产动环监控、边缘网关等智能物联网设备,广泛应用于 5G 基站、新能源等领域。半导体设备零部件项目以韩国团队为基础,建设半导体零部件研发生产、翻新及本土化供应链全链条体系。

(来源: 杭绍临空示范区绍兴片区)

## 晶能微电子:车规级SiC模块连续多月交付量超万套, 上车极氪全系产品

8月1日,浙江晶能微电子有限公司(以下简称"晶能")发文称,车规级 SiC 模块已实现连续多月交付量超万套,为极氪全系产品提供"动力芯"支持。

文章称,晶能微电子凭借在车规级功率半导体领域的技术积累,正将第三代半导体技术延伸至 eVTOL 和具身智能机器人产业。晶能在巩固新能源汽车领域优势的同时,积极开拓多元化应用场景。其中,SGT、IGBT、超结 MOS、SiC MOS 等多款分立器件已在电动两轮车、工业控制、充电桩等市场持续增长突破。

此前,晶能与正泰合资成立的泰芯半导体,旨在通过整合产业链优势,将业务场景拓展至光伏、储能、下一代 开关等新领域。

此外,吉利已战略布局沃飞长空、一星机器人等新兴产业。晶能将与沃飞长空、一星机器人以及宇树科技、松 延动力等行业头部公司战略协同,开发更具创新力的系统解决方案。

晶能 CEO 潘运滨表示,当前功率半导体行业正处于快速转型期,人工智能浪潮势不可挡,公司将继续坚持技术创新与应用落地并重的发展策略,通过持续优化产品性能、深化场景应用创新、加强产业链协同,为客户提供更具价值的解决方案,为新兴产业腾飞和全球绿色转型贡献力量。

(来源: 爱集微)

## 江丰电子: 拟与爱发科筹划整合双方平板显示靶材业务

8月15日,宁波江丰电子材料股份有限公司发布公告称,为优化业务结构,聚焦于半导体靶材和核心零部件主业,集中公司资源,加大研发和设备投入,加快突破"卡脖子"技术,进一步增强半导体业务核心价值,宁波江丰电子材料股份有限公司拟与日本株式会社爱发科(以下简称"爱发科")合作,整合双方平板显示靶材业务。本次整合事项尚处于筹划阶段,公司仍在调查论证过程中,暂未签署正式协议。

## 宁波江丰电子材料股份有限公司 关于与日本株式会社爱发科 共同筹划整合双方平板显示靶材业务的公告

本公司及董事会全体成员保证信息披露的内容真实、准确、完整,没有虚假

为优化业务结构,聚焦于半导体靶材和核心零部件主业,集中公司资源,加 大研发和设备投入,加快突破"卡脖子"技术,进一步增强半导体业务核心价值, 宁波江丰电子材料股份有限公司(以下简称"公司")拟与日本株式会社爱发科 (以下简称"爱发科")合作,整合双方平板显示靶材业务。

记载、误导性陈述或重大遗漏。

在平板显示靶材领域,公司拥有坚实的技术基础、成熟的研发团队,累积了 丰富的生产和管理经验,公司的平板显示靶材已通过国内知名平板显示器制造商 的认证,并实现了批量供货,客户端粘性强,订单具备可持续性。

爱发科是真空技术开创者,致力于研发和制造用于半导体、电子器件、平板显示的设备及材料,是历史悠久、世界知名的技术集团。爱发科是平板显示设备和靶材的创造者,在最先进的 OLED 靶材方面具有领先优势。

双方在平板显示靶材方面的整合,将充分发挥协同效应,实现资源共享、优 势互补、合作共赢,增强平板显示靶材产品在高端领域的技术实力与市场竞争力, 以期获得该业务的高质量发展。

本次整合事项尚处于筹划阶段,公司仍在调查论证过程中,暂未签署正式协议。本次整合的具体方案、实施进度等有关事项具有不确定性,敬请广大投资者 注意投资风险。

此项战略协同旨在充分融合双方核心技术优势与产业积淀。爱发科作为真空技术先驱,在先进 OLED 靶材研发制造领域底蕴深厚;江丰电子则长期专注于超高纯金属溅射靶材及半导体精密零部件的研发与生产,其平

板显示靶材已获国内知名制造商认证并稳定批量供应,客户基础稳固可靠。双方合作将显著增强高端平板显示靶材的技术实力,加速突破相关"卡脖子"技术环节,有力提升公司在半导体核心业务领域的价值创造能力。

市场拓展方面,江丰电子积极参与全球竞争,产品 已成功导入包括台积电、联华电子、中芯国际、韩国 SK 海力士、华虹宏力及京东方等在内的海内外顶尖半 导体与平板显示企业供应链,国际化布局稳步推进。

为持续满足市场需求、保障供给能力,公司产能建设有序进行: 黄湖靶材工厂主体工程顺利推进,设备安装调试正按计划展开; 半导体精密零部件多个生产基地陆续建成投产。为进一步增强核心产品供给能力,公司于今年7月发布定向增发预案,拟募集资金不超过人民币19.48亿元,重点投入"年产5100个集成电路设备用静电吸盘"及"年产1.23万个超大规模集成电路用超高纯金属溅射靶材"等关键产业化项目。

最新业绩预告显示,2025年上半年,江丰电子预计实现营业收入约21亿元,较上年同期增长约29%;实现归属于上市公司股东的净利润预计为2.47亿元至2.67亿元,同比增幅达53.29%至65.7%。国内外客户订单持续增长,充分印证了公司发展的强劲动能与产业链整体稳定性的全面提升。

本次整合事项尚处筹划阶段,具体实施方案与进度 存在不确定性。然江丰电子立足自主创新,深化国际合 作,其于关键材料领域的锐意进取,正为我国半导体与 显示产业的自主安全发展注入坚实力量,铺就一条以开 放合作锻造核心竞争力的进阶之路。

(来源:芯片说)

## 2025上半年浙江"415X"先进制造业集群规上营收创 新高

今年上半年,浙江"415X"先进制造业集群规上营收达 4.67 万亿元,同比增长 5%,高出面上工业 1.5个百分点,关键支柱作用凸显。

"415X"先进制造业集群是浙江"两新"深度融合的主战场,也是浙江特色现代化产业体系的主体。今年以来,浙江的集群运行稳进提质、向新向好,为确保高质量完成全年目标任务,更好发挥工业经济压舱石和支撑作用。

集群结构体系向新优化,传统产业、新兴产业、未来产业产业集群齐头并进。上半年,浙江一手抓传统产业转型升级,出台传统产业内生裂变若干举措,实施重点技改项目 5641 个,完成设备更新 7.32 万台(套),积极应对美加征关税,纺织服装、家具家电、绿色石化等传统产业集群顶住了压力; 一手抓新兴产业培育壮大,船舶海工、人工智能、新能源装备、智能物联、新能源汽车、高端软件、集成电路、机器人与数控机床等 8 个集群营收实现两位数增长。同时抓未来产业前瞻布局,累计培育未来产业先导区 22 家,24 个未来产业创新发展案例纳入工信部推广目录,居全国第一。

集群创新主战场地位稳固,研发投入稳步提升,创新成果加快涌现。上半年,"415X"先进制造业集群规上研发费用达 1601.1 亿元,同比增长 4.8%,占全省规上工业研发费用的 88%,较去年提升 0.7 个百分点;

研发费用占营收比重达 3.4%,高出工业面上 0.2 个百分点。同时,上半年集群新产品产值率达 42%, 工业机器人、锂离子电池、新能源汽车等产品产量保持 高位增长。

面向下一阶段的增长,集群后劲很足。一方面,生产效益有改善,有钱才有可持续的投入。上半年,集群规上利润总额 2353.2 亿元,同比增长 10.9%,高出工业面上 5.5 个百分点。像人工智能等 8 个集群实现利润两位数以上增长。另一方面,集群重大项目有序推进,

616 个总投资 10 亿元以上的集群重大制造业项目现已 完成投资 1287.8 亿元,纺织服装、新能源汽车、绿色 石化等集群投资完成率较高。138 个集群新建重大项目 开工率达 81.2%,如新能源汽车集群绍兴比亚迪半导 体功率器件、衢州极电三电系统等百亿级项目加快建 设,预计年内投产;新能源装备集群温州瑞浦兰钧年产 24GWh 动力与储能锂离子电池项目厂房建设基本完成。

在奋战三季度的关键时期,围绕全年力争"415X" 先进制造业集群规上营收突破9.5万亿元的目标,接下来,浙江一方面继续做好"两新"深度融合这篇大文章,一体推进传统产业焕新升级、新兴产业发展壮大、未来产业科学布局,加快出台新兴未来产业实施意见;另一方面持续打好集群培育"8个+"组合拳,加快构建"省级—国家级—世界级"梯度培育体系,全力争取世界级集群。

(来源:浙江经信)

## Q2全球TOP20芯片公司榜单

根据 WSTS 的数据,2025 年第二季度全球半导体市场规模为1800 亿美元,较2025 年第一季度增长7.8%,较2024 年第二季度增长19.6%。半导体情报表示,2025 年第二季度是连续第六个季度同比增长超过18%。

下表按收入列出了排名前二十的半导体公司。该名 单包括在公开市场上销售器件的公司,不包括台积电等 代工公司以及仅生产供内部使用的半导体的公司,例如 苹果。大多数情况下,收入指的是公司整体收入,其中 可能包含一些非半导体收入。如果单独列出收入,则使 用半导体收入。

根据英伟达预测,其 2025 年第二季度营收将达到 450 亿美元,因此仍是全球最大的半导体公司。存储芯片制造商三星和 SK 海力士分列二三位。博通排名第四,长期占据榜首的英特尔则跌至第五。

大多数公司报告称,2025年第二季度收入较第一季度稳健增长,加权平均增幅为7%。存储器公司增幅最大,其中SK海力士增长26%,美光科技增长16%,三星增长11%。

非存储器公司中,收入增幅最健康的是微芯片科技公司(11%)、意法半导体公司(10%)和德州仪器公司(9.3%)。五家公司的收入较 2025 年第一季度有所下降。

| 8                                             | Top Sem               | icond         | luctor (      | Compa            | nies' Revenue                     |

|-----------------------------------------------|-----------------------|---------------|---------------|------------------|-----------------------------------|

| Change versus prior quarter in local currency |                       |               |               |                  |                                   |

|                                               | Company               | US\$B<br>2Q25 | Reported 2Q25 | Guidance<br>3Q25 | Comments on 3Q25                  |

| 1                                             | Nvidia                | 45.0          | 2.1%          | n/a              | 2Q25 is 1Q25 guidance             |

| 2                                             | Samsung SC            | 19.9          | 11%           | n/a              | high-bandwidth memory strong      |

| 3                                             | SK Hynix              | 15.9          | 26%           | n/a              | demand strong                     |

| 4                                             | Broadcom              | 14.9          | -0.1%         | n/a              | 2Q25 is 1Q25 guidance             |

| 5                                             | Intel                 | 12.9          | 1.5%          | 1.9%             | strength in client, foundry down  |

| 6                                             | Micron                | 9.3           | 16%           | 20%              | strong demand for Al memory       |

| 7                                             | Qualcomm (IC)         | 9.0           | -5.0%         | 3.4%             | handset & auto up, IoT flat       |

| 8                                             | AMD                   | 7.7           | 3.3%          | 13%              | growth in client and data center  |

| 9                                             | MediaTek              | 4.9           | -1.9%         | -10%             | mobile down, global uncertainties |

| 10                                            | TI                    | 4.4           | 9.3%          | 4.0%             | auto weak, global uncertainties   |

| 11                                            | Infineon              | 4.2           | 3.1%          | 5.3%             | Al strong, auto weak              |

| 12                                            | NXP                   | 2.9           | 3.2%          | 7.7%             | auto, industrial & mobile up      |

| 13                                            | Sony                  | 2.8           | -0.2%         | n/a              | growth in mobile & digital camera |

| 14                                            | STMicro               | 2.8           | 10%           | 15%              | all end markets up except auto    |

| 15                                            | <b>Analog Devices</b> | 2.8           | 4.2%          | n/a              | 2Q25 is 1Q25 guidance             |

| 16                                            | Kioxia                | 2.4           | -1.2%         | 30%              | Al driving NAND growth            |

| 17                                            | Renesas               | 2.2           | 5.1%          | 1.7%             | auto flat, mobile & IoT up        |

| 18                                            | Marvell               | 2.0           | 5.5%          | n/a              | 2Q25 is 1Q25 guidance             |

| 19                                            | Onsemi                | 1.5           | 1.6%          | 3.2%             | auto & Al up, industrial down     |

| 20                                            | Microchip             | 1.1           | 11%           | 5.1%             | inventories too low               |

|                                               | Total of above        |               | 7%            | 8%               | companies with guidance for 3Q    |

几乎所有提供业绩指引的公司都预计,2025年第三季度的收入将较第二季度实现健康增长。其中,存储器公司再次实现最大增幅,美光公司预计增幅为20%,铠侠公司预计增幅为30%。两家公司均表示,人工智能应用的需求是关键驱动因素。

意法半导体(STMicroelectronics)预计其营收将增长 15%,除汽车市场外,所有终端市场均实现增长。AMD 预计在人工智能的推动下,其营收将增长 13%。其他六家公司提供的收入增长预期在 1.7% 至 7.7% 之间。唯一一家预计营收将下降的公司是联发科,由于移动市场疲软,其 2025 年第三季度的营收将下降 10%。

人工智能仍然是最大的增长动力。许多公司在其传统市场中看到了增长。一些公司的汽车收入正在增长,而另一些公司则认为汽车行业持续疲软。在与金融分析师的电话会议中,大多数公司都提到了关税和全球贸易方面的不确定性是令人担忧的领域。

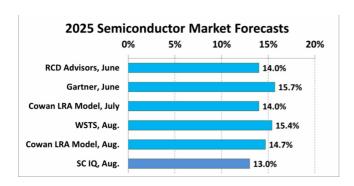

2025年上半年半导体市场的强劲增长几乎保证了全年两位数的增长。最近的预测普遍在 14% 至 16% 的窄幅区间内。WSTS 根据 2025年第二季度的数据,将其 6月份的预测从 11.2% 修正至 15.4%。

由于全球贸易的不确定性,半导体情报公司 (SC IQ) 仍持谨慎态度。但基于 2025 年上半年的强劲表现,该公司将 2025 年的预测从 5 月份的 7% 上调至 13%。

由于威胁征收的关税和已实施的关税频繁变化,预测美国关税对全球贸易的影响十分困难。就中国而言,特朗普政府在 4 月份威胁征收高达 145% 的关税。5 月份,特朗普政府暂停加征关税 90 天,并将对华关税定为 30%。本周,暂停加征关税的期限被延长至 11 月。

对半导体直接征收关税的不确定性很高。本月早些时候,特朗普总统宣布美国将对进口半导体征收 100%的关税。他表示,承诺在美国生产半导体的公司将不会面临关税。该计划的具体细节尚未公布。

本月,特朗普政府达成协议,为英伟达和 AMD 提供出口许可证,允许其向中国出口部分人工智能芯片。 两家公司将被要求将销售收入的 15% 上缴给美国政府。 该协议的合法性值得怀疑。

智能手机是已经受到关税影响的一个领域。近几个 月来,美国智能手机进口量急剧下降。2025年第二季度, 美国智能手机进口量以美元计算环比下降 58%,以数 量计算环比下降 47%。从中国进口的智能手机数量下 降了 85%。

尽管目前智能手机进口没有关税,但关税威胁已产生重大影响。Canalys 估计,2025 年第二季度美国智能手机销量将较第一季度下降约 20%。2025 年第二季度的销量很大一部分来自现有库存。

然而,美国智能手机销量在2025年下半年应该会

大幅下降。尽管对美出口下降,但中国智能手机制造业依然保持强劲,2025年第二季度的产量较2025年第一季度增长5%。

当前半导体市场表现强劲。持续的全球贸易争端令 人担忧,但迄今为止尚未产生实质性影响。

(来源:半导体产业纵横)

# 工信部:集成电路(上半年)产量+8.7%、出口+20.6%、设计+18.8%

8月1日工信部数据显示,2025年上半年我国电子信息制造业整体态势良好。规模以上企业增加值增11.1%,出口交货值增3.6%,营收8.04万亿元、利润3024亿元均增长;投资增4.6%略有下滑,区域营收分化,东、中部增长,西、东北部下降。集成电路表现亮眼,产量2395亿块增8.7%,出口1678亿个增20.6%,设计收入2022亿元增18.8%。

2025年上半年,集成电路相关数据如下:

- ·产量增长: 2025 年上半年集成电路产量 2395 亿块,同比增长 8.7%。

- ·出口增加:上半年我国出口集成电路 1678 亿个,同比增长 20.6%。

- ·设计收入增长: 上半年信息技术服务收入中,集成电路设计收入 2022 亿元,同比增长 18.8%。

#### 2025 年上半年电子信息制造业运行情况

2025 年上半年,我国电子信息制造业生产快速增长,出口稳定向好,效益持续改善,投资略有下滑,行业整体发展态势良好。

## 一、生产快速增长

上半年,规模以上电子信息制造业增加值同比增长 11.1%,增速分别比同期工业、高技术制造业高 4.7 个和 1.6 个百分点。6 月份,规模以上电子信息制造业增 加值同比增长 11%。主要产品中,手机产量 7.07 亿台,同比下降 4.5%,其中智能手机产量 5.63 亿台,同比增长 0.5%;微型计算机设备产量 1.66 亿台,同比增长 5.6%;集成电路产量 2395 亿块,同比增长 8.7%。

#### 二、出口稳定向好

上半年,规模以上电子信息制造业累计实现出口 交货值同比增长 3.6%,较 1—5 月提高 0.3 个百分点。 6 月份,规模以上电子信息制造业实现出口交货值同 比增长 5%。据海关统计,上半年,我国出口笔记本电 脑 6675 万台,同比下降 2.8%; 出口手机 3.4 亿台,同比下降 7%; 出口集成电路 1678 亿个,同比增长 20.6%。

## 三、效益持续改善

上半年,规模以上电子信息制造业实现营业收入8.04万亿元,同比增长9.4%;营业成本7.02万亿元,同比增长9.6%;实现利润总额3024亿元,同比增长3.5%;营业收入利润率为3.76%,较1—5月提高0.4个百分点。6月份,规模以上电子信息制造业营业收入1.55万亿元,同比增长9.6%。

## 四、投资略有下滑

上半年,电子信息制造业固定资产投资同比增长 4.6%,较 1—5 月回落 2.4 个百分点,比同期工业投资 增速低 5.7 个百分点。

#### 五、区域营收分化

上半年,规模以上电子信息制造业东部地区实现营业收入 57459 亿元,同比增长 11.3%; 较 1—5 月回落 0.5 个百分点; 中部地区实现营业收入 12936 亿元,同比增长 10.3%,较 1—5 月提高 0.7 个百分点; 西部地区实现营业收入 9632 亿元,同比下降 1.4%,较 1—5 月提高 1.8 个百分点; 东北地区实现营业收入 383 亿元,同比下降 4.9%,较 1—5 月回落 3 个百分点。6 月份,东部地区实现营业收入 11136 亿元,同比增长 9.3%;中部地区实现营业收入 2468 亿元,同比增长 13.5%;西部地区实现营业收入 1830 亿元,同比增长 7.2%;东北地区实现营业收入 33.9 亿元,同比增长 7.2%;东北地区实现营业收入 33.9 亿元,同比下降 27.4%。

(注: 1. 文中统计数据除注明外,其余均为国家统计局数据或据此测算。 2. 文中"电子信息制造业"与国民经济行业分类中的"计算机、通信和其他电子设备制造业"为同一口径。)

(来源:工信部)

## 中国FlipFET技术颠覆芯片

2025年,半导体行业正式叩响 GAA 时代。

随着 GAAFET 技术的落地,"逻辑芯片下一个大趋势"的光环也随之褪去。

三星在 3nm 中已应用 GAAFET 技术,台积电 也表示今年下半年大规模生产的 2nm 芯片中将应用 GAAFET 技术。

那么 GAA 之后,谁来接棒?按此前的技术路径,CFET 本是下一代架构的公认标杆。但随着 VLSI 2025 的启幕,中国北京大学提出的 FlipFET 技术,引起更大轰动。

## 01GAA 之后, 谁来接棒?

五十多年来,半导体行业一直依赖于一个简单的公式:缩小晶体管尺寸,将更多晶体管封装到每个晶圆上,然后看着性能飙升,成本骤降。

在 2D 晶体管时代,FinFET 是扛大旗者。

在此之前是 MOSFET,不过当栅极长度逼近 20nm 门槛时,对电流的控制能力急剧下降,漏电率也在升高, 传统的平面 MOSFET 正式走到尽头。

|        | MOSFET                                      | FinFET                                                 | GAAFET                                          |                                                   |  |

|--------|---------------------------------------------|--------------------------------------------------------|-------------------------------------------------|---------------------------------------------------|--|

| 名称     | 绝缘栅型场效应晶体管                                  | 鳍式场效应晶体管                                               | 环绕栅极场效应晶体管<br>(GAAFET)                          | 多桥通道场效应晶体管<br>(MBCFET)                            |  |

| 优点     |                                             | 相较MOSFET更好的渠道控制、抑制短通道效应、更快的切换速度、更高的漏极电流、较低的开关电压、更低的功耗。 | 并进一步增强栅极控制能力;寄生电<br>容和电阻问题得到改善;与FinFET结         | 可以提供更低的工作电压更<br>高的电流效率(即驱<br>动电流能力)和高度的设计<br>灵活性。 |  |

| 缺点     | 栅极长度逼近20nm门槛<br>时,对电流的控制能力急剧<br>下降,漏电率也在升高。 | 电压阈值难以控制、高寄生<br>效应;高电容、高成本。                            | GAAFET处于初步探索,工艺难度极<br>高给工艺控制带来更大的挑战;研发<br>成本攀升。 | 柵控能力不够强。                                          |  |

| 适用范围   | 28nm以上(物理极限)                                | 22nm-7nm(物理极限)                                         | 5nm以下                                           | -                                                 |  |

| 优先入局厂商 | -                                           | 英特尔                                                    | 三星                                              |                                                   |  |

2011 年,英特尔率先将 FinFET 技术商业化,并应用于 22nm 制程,显著提升性能与降低功耗。随后,台积电、三星等厂商跟进,FinFET 技术大放异彩。之后为了提高晶体管性能并进一步减小面积,FinFET 体系架构也进行了持续的改进。自 16/14nm 起,FinFET 成为主流选择。

步入 5nm 后,FinFET 就开始面临鳍片稳定性、栅极宽度限制及静电问题等挑战。FinFET 依靠"修修补补"又熬过两个制程节点。

进入 3nm 时代后,三星率先应用 GAAFET 技术, 台积电则相对保守,计划在 2nm 制程中投入应用。

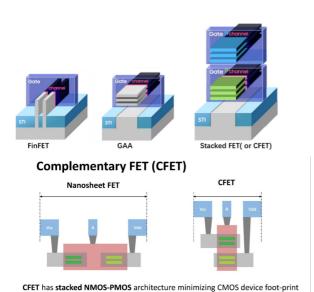

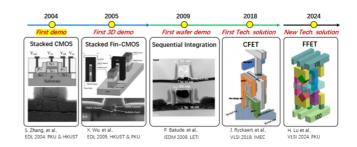

至于再下一代的三维晶体管结构,IMEC 于 2018年提出的补场效应晶体管(Complementary FET, CFET)被认为是一个有力的竞争者。

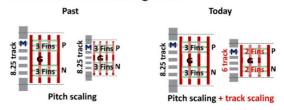

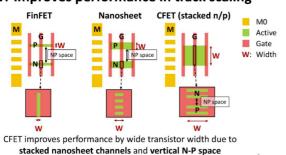

## **CMOS** standard scaling trend

CMOS standard cell scaling today driven by pitch scaling + track scaling (metal #/standard cell)

→ Performance degradation risk by Fin # reduction

图 1. 标准单元缩放

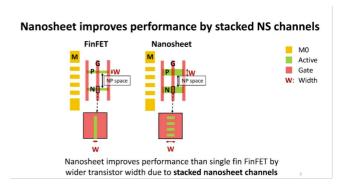

图 2 中显示通过从 FinFET 转向堆叠水平纳米片 (HNS),可以通过更宽的纳米片堆叠和垂直堆叠多个纳米片来改善/恢复性能。图 3 展示了但正如在 FinFET 中看到的那样,纳米片缩放最终会导致性能下降。

图 2. 纳米片的优势

# Nanosheet scaling limitation FinFET Nanosheet Nanosheet

如图 4,CFET 将不同导电沟道类型(N-FET 和P-FET)的 GAA 器件在垂直方向进行高密度三维单片集成。相较于 FinFET 与 GAAFET,CFET 突破了传统 N/P-FET 共平面布局间距的尺寸限制,可将集成电路中逻辑标准单元尺度微缩到 4-T(Track)高度,同时将减少 SRAM 单元面积 40% 以上。

图 3. 纳米片缩放限制

图 4.CFET 堆叠方式

如图 5,CFET 再次重置了缩放约束,因为 nFET 和 pFET 是堆叠的,器件之间的 n-p 间距变为垂直而不是水平,这使得图更宽。

#### **CFET improves performance in track scaling**

#### 图 5.CFET 改进的缩放比例

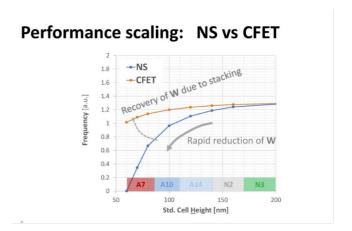

图 6 则比较了 HNS 和 CFET 性能与单元高度的关系,突出显示了 CFET 的优势。

图 6.HNS 与 CFET 性能与单元高度单片 CFET 与顺序 CFE

根据此前 IMEC 公布的技术路线图,**凭借 CFET,芯片工艺技术在 2032 年将有望进化到 5 埃米 (0.5nm),2036 年有望实现 2 埃米 (0.2nm)**。台积电、三星、英特尔等都在实验室中对 CFET 进行了预研开发。

如今 FlipFET 引发如此大规模的反响,部分原因在于其技术优势,甚至优于 CFET。

## 03FlipFET,优于 CFET

在去年 6 月召开的 VLSI 2024 上,北京大学吴恒研究员 - 黄如院士团队首次提出了 FlipFET 技术。

在今年的 VLSI 2025 上,黄如院士团队公布了新一代三维晶体管结构"倒装堆叠晶体管(Flip FET, FFET)",首次实现了 8 层晶体管的三维垂直集成,单位面积逻辑密度较传统 FinFET 提升 3.2 倍,功耗降低 58%。这一突破性成果被业界视为延续摩尔定律的

## 最具潜力方案之一。

FlipFET与 CFET 技术,存在根本上的差异。

FFET 技术的最大亮点之一在于**其独特的"双面有 源区+倒装+背靠背自对准"设计。**

CFET(互补场效应晶体管)是将 **n 型和 p 型晶体 管垂直堆叠在同一晶圆上,**共享同一栅极实现互补功能。 这种设计虽然能大幅缩小面积,但需要在同一晶圆上完成多层材料的精确对齐,制造复杂度极高。

不同于 CFET 依赖复杂的晶圆正面层叠工艺,FFET 先在晶圆正面制造 n 型晶体管(如 FinFET NMOS),再通过键合另一晶圆并翻转减薄,在背面制造 p 型晶体管(如 FinFET PMOS)。这种结构无需垂直堆叠,而是通过物理翻转实现 n/p 器件的空间分离,从根本上避免了 CFET 的多层对齐难题。

## 那么,FlipFET 破解了哪些 CFET 面临的 "老大难"问题?

第一,CFET 的垂直堆叠易导致漏电流路径增加,而 FlipFET 的双面布局天然隔离了 n/p 器件的漏极。

第二,CFET 的垂直堆叠需要极高的层间对齐精度,任何偏差都会导致电阻激增。FlipFET 通过自对准有源区和背面光刻校正技术,将关键对准误差控制在可接受范围内。

第三,CFET 的高温工艺限制了金属互连材料的选择,而 FlipFET 的低温流程允许保留成熟的铜互连技术。

第四,CFET 的固定堆叠结构难以适应不同应用场景,而 FlipFET 支持 "渐进式创新"。其不仅适用于Fin 结构的堆叠,还适用于下一代 GAA 纳米片,具有很强的拓展性。

FlipFET 技术备受关注意味着:在半导体技术领域,一个集成电路不仅可以在正面形成,还可以在背面形成的时代即将到来。

无独有偶,在此前的 IEDM2024 Press Kit 的《Paper 2.5, TSMC's Fully Functional Monolithic CFET Inverter at 48nm Gate Pitch》中,台积电在最新的 CFET 进展中也几乎同时引入了双面供电与双面信号互连的布局概念并实验展示了晶圆键合和翻转(Bonding + Flipping)技术的可行性,也证明了 FlipFET 技术涉及的极致晶圆减薄和双面光刻技术的可行性。

不过,从技术思路来看,二者存在根本上的差异,现有的正面 CFET 加背部互连的方式仍然延续了晶圆键合的传统三维集成方式,而 FFET 更倾向于等效利用晶圆的双面集成空间,从而拓展了器件与互连集成布局的适用范围,理论上具备了与平面集成方式一样的技术迭代能力,等同于三维版的等比例缩小法则。

虽然研究团队已经在硅片上演示了 FlipFET,但他们并未止步于此。他们展示并模拟了 FlipFET 设计的进一步创新,例如具有自对准栅极的 FlipFET、使用叉片(forksheet)并在隔离墙内嵌入电源轨的 FlipFET,甚至将 FlipFET 概念应用于具有高纵横比过孔的单片 CFET,以实现 4 堆叠晶体管设计。

当 FlipFET 的技术细节被公开时,它所带来的不仅是一项成果的亮相—— 更意味着中国在先进逻辑器件领域长期 "跟跑" 的态势被打破,全球半导体科研的话语体系里,从此有了更清晰的中国表达。这也引发台积电、英特尔等巨头的高度关注。台积电研发总监指出,该技术"重新定义了三维集成的技术边界"。

## 041nm 及以下芯片,在路上了

FlipFET 与 CFET 技术将会被用于未来更为尖端的 埃米级制程工艺。暂且不说 0.5nm,距离最近的 1nm 制程,还需要多久才能到来?

此前数据显示台积电计划在 2027 年达到 A14 节点,并在 2030 年达到 A10 节点,即 1nm 制程芯片。届时,采用台积电 3D 封装技术的芯片晶体管数量将超过 1 万亿个,而采用传统封装技术的芯片晶体管数量将超过 2000 亿个。

相比之下,采用 4nm 制程和传统芯片封装路径的 GH100 只有 800 亿个晶体管。

今年 2 月,市场消息称台积电正计划在中国台湾台南建设一座拥有最先进 1nm 工艺节点制程技术产线的

晶圆厂。据悉,这座新建的晶圆 25 厂将专注于生产 12 吋晶圆,工厂规模足够容纳 6 条产线。台积电已向南部科学园区管理处提交了相关计划,并透露了初步的产线配置。预计晶圆 25 厂的 P1 至 P3 产线将布置 1.4nm 制程技术,而 P4 至 P6 产线则将设置更为先进的 1nm 制程技术。

不过在台积电的 1nm 制程中,应该不会用到 CFET 工艺。毕竟在 2nm 制程中,台积电才刚刚用上 GAA 技术。 英特尔也是雄心勃勃,计划在 2025 年开始大规模生产基于 18A 制程技术的处理器,如果 18A 能够通过英伟达博通等设计厂商的验证测试,英特尔将大大提升自身的市场竞争力。英特尔官网显示,基于 Intel 18A 制程节点打造的首批产品 —— AI PC 客户端处理器 Panther Lake 和服务器处理器 Clearwater Forest,其样片现已出厂、上电运行并顺利启动操作系统。

英特尔 18A 制程采用了 RibbonFET 环绕栅(GAA)晶体管技术,相比此前的 FinFET 技术实现重大飞跃,不仅改进了栅极静电,单位封装的宽度更高,单位封装的寄生电容也更小,灵活性也更高。

英特尔的目标则是在 2025 年将 Intel 18A 推向市场。根据外部预测,18A 进入量产预计在 2025 年年中,上市则可能要等到今年下半年。

IBM 正寻求与日本 Rapidus 公司建立长期合作伙伴关系,共同开发 1 纳米以下芯片。在 2 纳米合作的基础上,IBM 已向 Rapidus 位于北海道的工厂派遣工程师,标志着两家公司在追求下一代半导体生产以及日本加大对芯片创新投资的背景下,双方的合作关系将更加深入。

(来源: 半导体产业纵横)

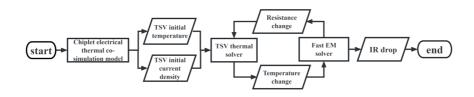

## 中科院微电子所在芯粒集成电迁移EDA工具研究方向取 得重要进展

随着高性能人工智能算法的快速发展,芯粒(Chiplet)集成系统凭借其满足海量数据传输需求的能力,已成为极具前景的技术方案。该技术能够提供高速互连和大带宽,减少跨封装互连,具备低成本、高性能等显著优势,获得广泛青睐。但芯粒集成中普遍存在供电电流大、散热困难等问题,导致其面临严峻的电迁移可靠性挑战。针对工艺层次高度复杂的芯粒集成系统,如何实现电迁移问题的精确高效仿真,并完成电迁移效应与热效应的耦合分析,已成为先进封装可靠性 EDA 工具领域的重点研究方向。

为应对上述挑战,中国科学院微电子研究所 EDA 中心孙泽宇研究员与徐勤志研究员团队合作开发了一种针对芯 粒集成系统中 TSV 互连的电迁移 - 热耦合仿真模型。该模型利用时域有限差分法(FDTD),建立了一套涵盖电迁 移空洞成核期与完整生长过程的全流程电 - 热 - 应力综合分析方法,能够精确计算电子流导致的静水应力。研究还 构建了包含散热器的异质集成系统全芯片热模型,应用有限体积元方法(FVM)进行全局电热协同仿真,在严格遵 循热传导方程守恒原理的同时,大幅提升了计算效率。尤为关键的是,该模型通过整合电迁移 - 热迁移与焦耳热效 应的仿真,能够在统一框架下解析应力演变、空洞生长、电阻变化和焦耳热效应之间的相互作用机制。模型验证结果表明,与业界商用有限元工具 COMSOL 相比,仿真误差仅为 0.61%;与实验数据相比,其电迁移寿命预测误差较现有主流方法显著降低了 76.4%。该模型还能准确反映不同分析阶段温度和电流密度对电迁移过程的主导作用。

此项研究成果以"ChipletEM: Physics-Based 2.5D and 3D Chiplet Heterogeneous Integration Electromigration Signoff Tool Using Coupled Stress and Thermal Simulation"为题,在第62届国际设计自动化会议(DAC)上进行了口头报告。孙泽宇研究员为论文第一作者,徐勤志研究员和微电子所 EDA 中心李志强研究员为共同通讯作者。该研究工作获得了中国科学院战略性 A 类先导专项、国家自然科学基金、中国科学院青年交叉团队等项目的资助。

图 1: 整体电迁移仿真流程

图 2: 电迁移应力分析结果

图 3: 不同时间段电迁移整体应力分布

(来源:中国科学院微电子研究所)

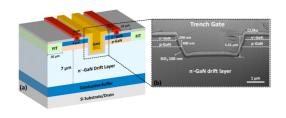

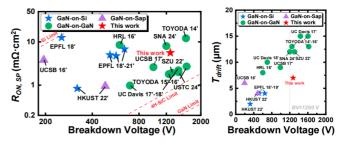

## 垂直氮化镓重磅发布

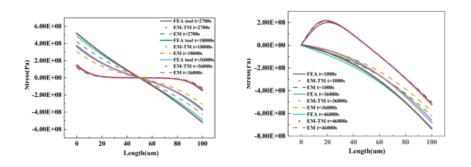

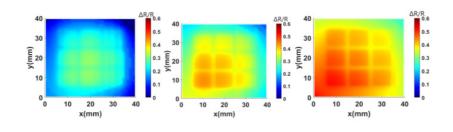

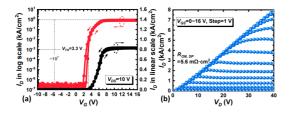

近日,山东大学发布了一篇题为《1200 V Fully-Vertical GaN-on-Si Power MOSFET》的论文。在文中,他们介绍一种 1200 V 全垂直 GaN-on-Si 沟槽 MOSFET,采用氟注入终端(FIT-MOS)。FIT(fluorine implanted termination)区由于带有固定的负电荷而表现为高电阻,可自然地将分立器件隔离,取代了传统的台面刻蚀终端(MET),消除了台面边缘的电场拥挤效应。

结果显示, FIT-MOS 的击穿电压从 MET-MOS 的

Y. Ma et al.: 1200 V Fully-Vertical GaN-on-Si MOSFET

#### 1200 V Fully-Vertical GaN-on-Si Power MOSFET

Yuchuan Ma, Hang Chen, Shuhui Zhang, Huantao Duan, Bin Hu, Huimei Ma, Jianfei Shen, Minghua Zhu, Jin Rao and Chao Liu

567 V 提升至 1277 V。此外,所制备的 FIT-MOS 具有 3.3 V 的阈值电压 (Vth)、约  $10^7$  的开关比 (ON/OFF ratio),以及  $5.6 \text{ m}\Omega\cdot\text{cm}^2$  的比导通电阻 (Ron,sp)。这 些结果表明,GaN-on-Si 垂直晶体管在 kV 级应用中具 有巨大的性价比潜力。

#### 简介

氮化镓(GaN)和碳化硅(SiC)等宽禁带半导体,在开发高效、高密度电力系统方面具有巨大潜力。目前,GaN 基晶体管已广泛应用于 100 V 至 650 V 的电源,而SiC 基晶体管则主要在 1200 V 以上的高压领域占据商业主导地位。

然而,对于 650 V 至 1200 V 这一对成本和性能竞争都异常激烈的市场区间, GaN 和 SiC 谁将成为最佳选择,仍未可知。尽管 SiC 基晶体管的发展取得了显著进展,但其相对高昂的衬底成本,从经济角度限制了它们在这一电压范围内的竞争力。

幸运的是,在低成本、大尺寸硅(Si)衬底上外延 生长 GaN 的异质外延技术取得了突破,这为制造高性 价比、高性能的 GaN 晶体管带来了巨大希望。 得益于 AlGaN/GaN 异质界面处产生的高密度二维电子气(2DEG),GaN 基横向高电子迁移率晶体管(HEMTs)在需要高频率和低电压的应用中具有显著优势。然而,由于横向架构固有的可扩展性限制,将GaN-on-Si 横向 HEMT 的击穿电压扩展到 650 V 以上仍然是一个挑战。

相比之下,垂直拓扑结构具有设计灵活性,垂直 GaN 功率晶体管通过增加漂移层的厚度而不增加器件 的面积,在千伏(kV)级阻断能力方面展现出显著优势。近年来,已成功开发出多款 1200 V 垂直 P-i-N 二极管,并展示了优异的阻断和雪崩能力,这验证了垂直 GaN-on-Si 拓扑在高压和高功率应用中的可行性。

Liu 等人首次报道了准垂直 GaN-on-Si 沟槽 MOSFET,采用 4 μm 厚的 GaN 漂移层,其硬击穿电压达 645 V。随后研究聚焦于优化 p-GaN 沟道区与栅介质层,以改善准垂直 GaN-on-Si 沟槽 MOSFET 的导通性能和可靠性。为消除准垂直结构中存在的电流拥挤效应,Khadar 等人展示了首个全垂直 GaN-on-Si 沟槽 MOSFET,其漏极电极沉积于通过选择性去除缓冲层和硅衬底后暴露的背面 n+-GaN 层上。Debaleen 等人报道了一种带有导电缓冲层的全垂直 GaN-on-Si 晶体管,这种设计消除了复杂的衬底工艺并简化了制造流程。然而,由于缺乏有效的终端结构和高质量的漂移层,这些报道的垂直 GaN-on-Si MOSFETs 的击穿电压(BV)仍低于 650 V,这对于千伏(kV)级别的电力系统应用来说是不足的。

本文展示了一种 1200 V 全垂直 GaN-on-Si 沟槽 MOSFET,采用氟离子注入终端(FIT)。传统的台面 刻蚀终端(MET)被高阻的 FIT 结构取代,该结构能够 有效隔离分立器件,并缓解终端区域的电场拥挤效应。 因此,FIT-MOS 的击穿电压从 MET-MOS 的 567 V 提升至 1277 V。此外,FIT-MOS 表现出增强型工作模式,具有 3.3 V 的阈值电压 (Vth)、约 107 的开关比 (ON/OFF

ratio)、低的比导通电阻 (Ron,sp) 为  $5.6~\text{m}\Omega\cdot\text{cm}^2$ ,以 及  $8~\text{kA/cm}^2$  的高导通电流密度。这些结果为基于 GaNon-Si 垂直晶体管的 kV 级电力电子系统的发展奠定了基础。

#### 外延生长与器件制造

图 1(a)-(b) 展示了全垂直 GaN-on-Si FIT-MOS 的结构示意图和沟槽栅区域的截面扫描电子显微镜(SEM)图像。通过注入强电负性的氟离子,原本导电的 n+GaN/p-GaN 层在 FIT 区域内变为高阻层,从而有效地隔离分立 FIT-MOS 器件,消除了传统 MET 结构的需求。FIT-MOS 的栅沟槽深度为  $1.15~\mu m$ ,延伸至 n-GaN 漂移层。可以观察到完整的栅堆叠结构,包括 100~nm 厚的  $SiO_2$  栅介质层,以及 50/150~nm 厚的 Cr/Au 栅金属层。

图 1: (a) 全垂直 GaN-on-Si 沟槽 MOSFET 的结构示意图; (b) 带氟注入终端 (FIT-MOS) 的沟槽栅区域横截面 SEM 图像

FIT-MOS 的制造工艺首先使用 SiO<sub>2</sub> 作为硬掩膜进行栅沟槽刻蚀,随后在氮气环境下以 850° C 快速热退火(RTA)20 分钟,以激活埋藏的 p-GaN 层中的受主。通过在 25% TMAH 溶液中 85° C 浸泡 3 小时修复干法刻蚀损伤。随后进行三次氟离子注入(能量 / 剂量:240 keV/4×10<sup>14</sup>cm<sup>-2</sup>,140 keV/2×10<sup>14</sup>cm<sup>-2</sup>,80 keV/1.2×10<sup>14</sup>cm<sup>-2</sup>),采用住友 Eaton Nova 的 NV-GSD-HE 离子注入机,并用约  $6.5\mu m$  厚的 AZ4620 光刻胶作为掩膜,形成 FIT 区域。

随后采用原子层沉积(ALD)沉积 100 nm 厚的 SiO<sub>2</sub> 栅介质层,并通过反应离子刻蚀(RIE)开源极接触孔。最后沉积双层 Cr/Au 堆叠以形成栅极和源极电极。低电阻硅衬底作为漏极电极。MET-MOS 与 FIT-MOS 的工艺流程类似,不同之处在于 MET-MOS 采用台面刻蚀来隔离分立器件。

## 结果与讨论

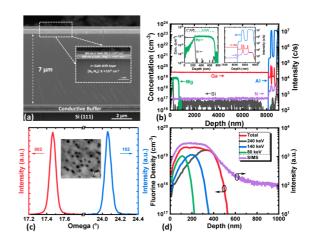

图 2(a)-(b) 展示了全垂直沟槽 MOSFET 的 N-P-N 外延结构的截面 SEM 图像及二次离子质谱 (SIMS) 剖面。

从上到下,N-P-N 结构包括:20nm 厚的  $n^{++}$ -GaN 层(Si 掺杂  $\sim$ 1×10<sup>19</sup>cm<sup>-3</sup>)、200 nm 厚的  $n^{+}$ -GaN 源极接触 层(Si 掺杂  $\sim$ 5×10<sup>18</sup>cm<sup>-3</sup>)、400nm 厚的 p-GaN 沟道 层(Mg 掺杂  $\sim$ 1×10<sup>19</sup>cm<sup>-3</sup>)、以及  $7\mu$ m 厚的  $n^{-+}$ -GaN 漂移层(ND-NA  $\sim$ 8×10<sup>15</sup>cm<sup>-3</sup>)。该结构外延在 6 英寸 Si 衬底上,并采用导电缓冲层,通过金属有机化学气相沉积(MOCVD)实现。

图 2(a) 全垂直沟槽型 MOSFET 的 N-P-N 外延结构的横截面扫描电子显微镜

(SEM) 图像; (b) 全垂直沟槽型 MOSFET 的 N-P-N 外延结构的二次离子质谱(SIMS) 剖面图; (c) (002) 和 (102) 晶向的 Omega 摇摆曲线。插图显示了在Si 衬底上生长的 GaN 层;阴极发光(CL) 图像; (d) 通过物质中离子输运 (TRIM) 模拟和二次离子质谱(SIMS) 测量得到的氟离子(F离子)分布

导电缓冲层由 AlGaN/AlN 多层组成,可实现全垂直电流通路,同时避免复杂的衬底工程工艺。而且,基于 AlGaN/AlN 的缓冲层还能对上方的 GaN 漂移层提供足够的压应力,有效补偿拉伸应力,避免因高温冷却过程引起的裂纹。通过 X 射线  $\omega$  摇摆曲线的半峰宽(FWHM)(见图 2(c)),估算出的穿通位错密度(TDD)为  $3.0 \times 10^8 cm^{-2}$ ,其计算公式如下:

$$D = \frac{\beta_{(002)}^2}{9\overline{b_1}^2} + \frac{\beta_{(102)}^2}{9\overline{b_2}^2}$$

其中, $\beta$  是半峰宽,b 是伯格斯矢量。通过阴极发光(CL)测量也得到了类似的位错密度(TDD),为  $1.4\times10^8$  cm<sup>-2</sup>,如图 2(c) 的插图所示。图 2(d) 显示了通过物质中离子输运 (TRIM) 模拟和 二次离子质谱 (SIMS) 测量得到的氟离子(F离子)分布剖面,结果显示氟离

子在 FIT 结构中呈均匀分布。

图 3(a) 显示了 FIT-MOS 在 VDS = 10 V 下的转移特性曲线(线性与对数坐标)。FIT-MOS 表现为增强型工作模式,具有正的阈值电压 Vth = 3.3 V (在 IDS =  $1 \text{ A/cm}^2$  时提取)、约  $10^7$  的开关比,以及  $\sim 0.5 \text{ V}$  的迟滞现象。图 3(b) 显示了所制备 FIT-MOS 的输出特性,揭示其高导通电流密度为  $8 \text{ kA/cm}^2$ 。由线性区计算得到的比导通电阻 Ron,sp 约为  $5.6 \text{ m}\Omega\cdot\text{cm}^2$ 。

图 3(a) 所制造的全垂直 GaN-on-Si FIT-MOS 的转移特性曲线;(b) 所制造的全垂直 GaN-on-Si FIT-MOS 的输出 I-V 特性曲线。ID(漏极电流)已按沟槽面积进行归一化

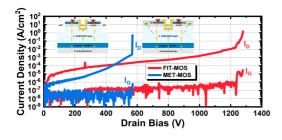

图 4 对比了 FIT-MOS 与 MET-MOS 的关断态击穿特性。在击穿前,栅漏电流 (IG) 始终低于 10-6 A/cm²,表明栅介质堆叠在高漏极偏压下具有优异的稳定性。FIT-MOS 的击穿电压高达 1277 V,而 MET-MOS 在 567 V就发生了过早击穿。在低 VDS 时,FIT-MOS 的关断态电流密度比 MET-MOS 更大,这是由于 FIT 结构引入了额外的纵向漏电通道。这一现象可通过测试结构的点对点漏电流密度(见图 5(a))得到验证。此外,由于氟离子注入后 FIT 区域存在 Ga 空位、原子键合不足以及能量约束不足,氟离子可能在 GaN 晶格中扩散并逸出表面,从而影响器件的热稳定性。采用优化的后注入退火工艺可有效降低关断态漏电流密度,并增强 FIT-MOS的热稳定性。

图 4,在 VGS=0 V 条件下,所制造的全垂直 GaN-on-Si FIT-MOS 和 MET-MOS 的关态击穿 I-V 特性曲线。插图显示了 FIT-MOS 和 MET-MOS 的潜在漏电路径

图 5(a) 带有 FIT 和 MET 隔离的测试结构 (插图) 的电极到电极的漏电流密度, (b) MET-MOS 在 VDS=400 V 时的模拟电场分布; (c) FIT-MOS 在 VDS=1200 V 时的模拟电场分布

为分析 MET-MOS 和 FIT-MOS 的击穿机理,采用 TCAD 仿真计算二维电场分布(见图 5(b)-(c))。仿真中使用的关键物理模型包括载流子漂移扩散模型、产生-复合模型、连续性方程与泊松方程,以及碰撞离化模型。在 VDS = 400 V 时,MET 结构在台面拐角处可观察到电场拥挤,峰值电场达 2.7 MV/cm,导致其击穿电压下降。而如图 5(c) 所示,FIT 结构能够有效抑制终端区域的电场拥挤。然而,在沟槽栅区域仍观察到电场拥挤,这可以通过采用栅极屏蔽结构来有效抑制。

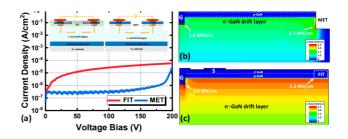

图 6: (a) 比导通电阻 Ron,sp 与击穿电压 BV 的对比; (b) 漂移层厚度 (Tdrift) 与击穿电压 BV 的对比。对比对象为本文制备的 GaN-on-Si 全垂直 FIT-MOS 与

已报道的在 Si、蓝宝石 (Sap) 和 GaN 衬底上的 GaN 垂直沟槽 MOSFET

图 6(a)-(b) 对比了本文制备的 GaN-on-Si FIT-MOS 与已报道的在 Si、蓝宝石 (Sap) 和 GaN 衬底上制备的垂直 GaN 沟槽 MOSFET 的 Ron,sp-BV 以及漂移层厚度 -BV 特性。本文 FIT-MOS 在异质衬底(Si 与 Sap)上实现了先进水平的击穿电压 1277 V,低比导通电阻 5.6 m $\Omega$ ·cm²,以及高 Baliga 优值(BFOM = BV² / Ron,sp)为 291 MW/cm²,其性能与在本征 GaN 衬底上制备的器件相当。此外,得益于高效的氟注入终端技术,7  $\mu$ m 漂移层厚度的 GaN-on-Si 全垂直 FIT-MOS 实现了与典型 1200 V 级 GaN-on-GaN 垂直沟槽 MOSFET相当的击穿电压,而后者通常需要超过 10  $\mu$ m 的漂移层厚度。这一结果标志着低成本 GaN-on-Si 垂直

MOSFET 向 1200 V 级电力应用迈出了关键一步。

#### 结论

本文展示了一种 1200 V 全垂直 GaN-on-Si 沟槽 MOSFET,采用氟离子注入终端(FIT)技术。FIT 结构取代了常规的台面刻蚀终端,有效地实现了对离散 FIT-MOS 器件的隔离,从而消除了 MET-MOS 中的电场

拥挤效应。结果实现了 1277 V 的先进击穿电压,以及 291 MW/cm² 的 Baliga 优值 (BFOM)。氟注入终端技术 为垂直 GaN 沟槽 MOSFET 在 kV 级电力系统中的应用 展现了巨大的潜力。

(来源: IEEE)

## 九峰山实验室首发6英寸InP激光器与探测器外延工艺

九峰山实验室首发 6 英寸 InP 激光器与探测器外延工艺

九峰山实验室近日在磷化铟(InP)材料领域取得 重要技术突破,成功开发出6英寸磷化铟(InP)基 PIN 结构探测器和 FP 结构激光器的外延生长工艺,关 键性能指标达到国际领先水平。这一成果也是国内首次 在大尺寸磷化铟材料制备领域实现从核心装备到关键材 料的国产化协同应用,为光电子器件产业化发展提供重 要支撑。

九峰山实验室 6 英寸磷化铟 PIN 探测器外延片

作为**光通信、量子计算等领域的核心材料,磷化铟** (InP) 材料的产业化应用长期面临大尺寸制备的技术 瓶颈,业界主流停留在 3 英寸工艺阶段,高昂的成本使 其无法满足下游产业应用的爆发式增长。

九峰山实验室依托国产 MOCVD 设备与 InP 衬底技

术,突破大尺寸外延均匀性控制难题,首次开发出6英寸磷化铟(InP)基PIN结构探测器和FP结构激光器的外延生长工艺,关键性能指标达到国际领先水平,为实现6英寸磷化铟(InP)光芯片的规模化制备打下基础。

## 材料性能:

- FP 激 光 器 量 子 阱 PL 发 光 波 长 片 内 标 准 差<1.5nm,组分与厚度均匀性<1.5%

- PIN 探测器材料本底浓度 <4×10<sup>14</sup>cm<sup>-3</sup>,迁移率 >11000 cm<sup>2</sup>/V·s

在全球光电子产业高速发展的背景下,光通信、激光雷达、太赫兹通信等领域对磷化铟(InP)的需求呈现爆发式增长。据 Yole 预测,磷化铟(InP)光电子市场规模 2027 年将达 56 亿美元,年复合增长率(CAGR)

达 14%。6 英寸磷化铟(InP)工艺的突破,有望推动 国产光芯片成本降至 3 英寸工艺的 60%-70%,有助于 增强国产光芯片市场竞争力。

九峰山实验室本次联合国内供应链实现**全链路突破,**对促进我国化合物半导体产业链协同发展有着重要影响,也为产业链自主可控奠定了基础。例如,九峰山实验室本次技术突破中6英寸磷化铟(InP)衬底合作方云南鑫耀的6英寸高品质磷化铟单晶片产业化关键技

术已实现突破,量产在即。未来,实验室将持续优化 6 英寸 InP 外延平台,推动下游产品验证,提升产业链自 主可控能力,推动我国光电子产业升级。

(来源:九峰山实验室)

## 中国算力规模全球第二,AI专利数占全球六成

今日国务院新闻办公室举行"高质量完成'十四五'规划"系列主题新闻发布会,介绍"十四五"时期数字中国建设发展成就。

"十四五"时期**我国数字基础设施实现长足发展。 我国数字基础设施在规模、技术等方面处于世界领先地位,**截至 2025 年 6 月底,5G 基站总数达到 455 万个,**千兆宽带用户达 2.26 亿户,算力总规模位居全球第二。**

经过多年持续攻坚,我国在数字领域突破了一批关键核心技术,展示出我国显著的发展成绩。集成电路加快布局,形成覆盖设计、制造、封装测试、装备材料的完整产业链;**国产操作系统加速崛起,鸿蒙系统生态设备总量突破 11.9 亿台,**为手机、汽车、家电等 1200 多类产品装上"智能中枢";我国人工智能综合实力实现整体性、系统性跃升,**人工智能专利数量占全球总量的 60%**。

我国去年推出了公共数据资源开发利用等 21 项政策,**今年还将推出数据产权等 10 多项制度,**一批围绕数据汇聚共享、开发利用的数据企业正在孕育兴起,标准、规范不断推出,数据交易日趋活跃,**全国一体化数据市场正在加快构建**。

据国家数据发展研究院的研究数据,2024年,**全** 国数据企业数量超 40 万家,数据产业规模达 5.86 万亿

元,较"十三五"末增长117%,预计未来几年仍将保持较高的增长水平。

截至目前,全国已建成包含北上广深等 25 个城市 在内的数据流通节点城市,布局了 16 个省市区的数据 基础设施架构,并在今年 7 月底全面完成了互联互通。 预计到今年年底,相关节点城市规模将扩大到 50 个左 右,覆盖 80% 的省市区,为数据规模化跨域流通奠定 设施基础。

经过一段时间的努力,**国内多数模型使用的中文数据占比已超过60%,有的模型已达到80%。**中文高质量数据的开发和供给能力持续增强,使得我国模型性能快速提升。

在数据市场"软环境"建设方面,国家数据局积极 推动数据交易机构的优化布局和进一步整合,同步推动 数据交易机构互认、互通。目前在北京、上海、浙江等 地已实现数据产品"一地上架,全国互认"。

2024 年我国数据生产量达 41.06 泽字节(计算机存储容量单位,简称 ZB,1ZB 大约等于 1 万亿 GB),纵向看较"十三五"末翻了一番多,横向看在全球占比达 26.67%。人均数据生产量是"十三五"末的 2.2 倍。

当前,我国网民数量达到 11.23 亿人,互联网普及率达到 79.7%,在各部门、各地区共同努力下,用得上、

用得起、用得好的数字服务正惠及更多百姓。

智慧医疗服务扩面提速,全国互联网医院年服务量超过1亿人次,**全国医保码用户超过12亿人,跨省异地就医直接结算惠及5.6亿人次。**

我国已建成全球规模最大、资源最丰富的国家智慧 教育平台,**慕课也就是大规模开放在线课程,建设数量 和应用规模都居世界第一。**

随着智能算力需求增长,多方正积极部署进一步提升智能算力供给能力。工信部相关负责人近日表示,将加强智算引领,优化算力结构。积极推进人工智能计算架构和软件生态建设,加速突破一批标志性技术产品和方案,鼓励各方主体探索智能计算中心建设运营新模式。

此外,多地也纷纷出台专项规划,明确未来几年建设目标,并在技术、应用、资金等方面完善支持举措。

例如,江苏发布省级算力基础设施发展专项规划,提出 到 2030 年全省在用总算力超过 50EFLOPS(EFLOPS 是指每秒百亿亿次浮点运算次数),智能算力占比超过 45%;甘肃提出对算力网络新型基础设施在用地、市政 配套设施建设、人才引进、资金等方面给予政策支持。

业内人士认为,算力基础设施创新发展有望带动数字经济相关产业增长,为经济增长注入新动能。有关研究表明,计算力指数平均每提高1个百分点,数字经济和国内生产总值(GDP)将分别增长3.3%和1.8%。

值得一提的是,按照今年政府工作报告提出的"适度超前建设数字基础设施,加快形成全国一体化算力体系"部署,多方在夯实算力发展基础的同时,也在算力互联上展开探索。

(来源:新华社)

## 光置技术的较量

当一颗指甲盖大小的芯片里塞进百亿个晶体管时,很少有人会追问:这些比细菌还小的电路图案,最初是怎么"画"出来的?答案藏在一块看似普通的石英玻璃背后——光罩,这个被业内称为"半导体母版"的关键器件,正以纳米级的精度定义着芯片的极限性能。

## 01 光罩三百年进化史

如果回溯光罩的前世今生,会发现它的进化史就是一部微观制造的精度竞赛史。18世纪末,法国人约瑟夫·尼塞福尔·涅普斯用沥青涂层的锡版制作了世界上第一块"光罩",通过日光曝光将窗外景色印在金属板上——这种原始的成像逻辑,与今天半导体光罩惊人地相似。只是当年的"像素"是毫米级的色块,而今已缩小到 0.5 纳米,相当于把地球按比例缩小到乒乓球大小的精度控制。

1990 年代末,随着半导体进入深亚微米时代,光 罩技术迎来最剧烈的变革期。KrF(248nm)光刻技术 要求光罩线宽达到 180nm,这意味着需要检测直径仅 50nm 的缺陷 —— 相当于在标准足球场大小的区域内 找出一颗尘埃。为应对挑战,光罩制造引入了原子层沉积 (ALD) 技术,实现铬层厚度控制在 ±0.1nm 范围内;同时开发了激光修复系统,通过聚焦离子束(FIB)精确移除缺陷,修复精度达 10nm 级。

现代光罩的核心结构看似简单:在高纯度石英玻璃上,用铬层蚀刻出电路图案。但在实际制造中,这块"玻璃片"需要经过30多道工序的雕琢。日本信越化学生产的光罩基板,每平方厘米的平整度误差不能超过0.3纳米。

2024 年三星推出的 3nm GAA 工艺中,光罩技术实现了一次关键突破:采用"自对准多重曝光"(SAQP)技术的光罩组,通过四次叠加曝光,在物理分辨率有限的情况下,"画"出了间距仅 7nm 的鳍片场效应晶体管(FinFET)。这就像用 4 张不同角度的底片,在同

一张相纸上叠加出立体影像,只不过这里的"相纸"是单晶硅,"影像"是能导电的纳米结构。

| 时间节点   | 关键技术                  | 最小线宽    | 代表应用        |  |

|--------|-----------------------|---------|-------------|--|

| 1826年  | 沥青锡版光罩                | 1mm     | 早期摄影        |  |

| 1959 年 | 镀铬玻璃光罩                | 10 µ m  | 第一代集成电路     |  |

| 1978年  | g线光刻光罩                | 2 µ m   | 8086 处理器    |  |

| 1989年  | i 线相移光 <mark>罩</mark> | 0,5 μ m | 486 处理器     |  |

| 1997年  | KrF 电子束光罩             | 180nm   | Pentium III |  |

| 2004年  | ArF 浸没式光罩             | 45nm    | iPhone 芯片   |  |

| 2018年  | EUV 反射光罩              | 7nm     | 5G 基站芯片     |  |

| 2024年  | SAQP 光罩组              | 3nm     | 3nm GAA 晶体管 |  |

#### 02 产业链的"咽喉要道"

光刻工艺堪称半导体器件制造工艺的核心步骤之一,光刻成本约占整个硅片制造工艺的 1/3,耗费时间约占整个硅片工艺的 40%-60%,而光罩在其中扮演着无可替代的"投影模版"角色。其工作流程极为精密复杂,首先由特定光源发出光线,如 248nm 的 KrF(氟化氪)准分子激光常用于 90nm 至 0.25μm 制程节点,193nm 的 ArF(氟化氩)准分子激光则支撑着从 65nm 到目前先进的 3nm 制程。光线透过光罩的透明区域,这里的透明区域与遮光区域由铬层等材料精准界定,进而将光罩上精心设计的电路图案投影到涂有光刻胶的晶圆表面,这一关键步骤即为曝光。

在曝光过程中,光刻胶会因吸收光子能量而发生光 化学反应。对于正性光刻胶,曝光区域的光刻胶在显影 液中溶解度大增;负性光刻胶则相反,未曝光区域在显 影液中溶解。经显影处理后,晶圆表面便形成与光罩一 致的图案。此后,利用刻蚀工艺,如等离子体刻蚀,通 过高能离子束对晶圆进行轰击,将显影后的光刻胶图案 转移到晶圆上的特定材料层,去除不需要的材料部分, 留下所需的电路结构。

值得一提的是,光罩上的图案一般是电路设计图的 4 倍大小,这种放大设计便于在光罩制作阶段对图案进行更精准的加工与修正。通过光刻机先进的投影系统,如采用多组高精度透镜组成的光学系统,将光罩图案缩小到 1/4 后投影到晶圆上。这种缩小操作基于光学成

像原理,不仅提高了分辨率,理论上分辨率与曝光波长成正比,与投影系统的数值孔径成反比,缩小图案相当于变相缩短了曝光波长,还降低了制造误差。因为在缩小过程中,图案边缘的微小偏差被大幅缩小,使得最终在晶圆上形成的电路图案更为精准。

可以形象地说,光罩就如同投影仪的"幻灯片",借助光的投射,把图案清晰地映射到 "屏幕" —— 晶圆之上。但与普通幻灯片不同,光罩制作需历经 30 多道工序,从高纯度石英玻璃基板的选择,像日本信越化学生产的光罩基板,每平方厘米的平整度误差不能超过0.3 纳米,到铬层等遮光层的精准蚀刻,再到图案的电子束或激光直写绘制,每一步都对精度和环境洁净度有着严苛要求,其复杂程度和技术门槛极高,是半导体制造中名副其实的 "咽喉要道",决定着芯片制造的精度与性能。

## 03 谁在掌控光罩话语权?

掌握高端光罩,尤其是 EUV 光罩的核心技术与制造能力,已成为决定先进芯片制造话语权的关键一环。 当前,这一领域的竞争格局高度集中,少数几家掌握顶 尖技术的企业牢牢把控着产业链的关键节点。

审视全球光罩产业链,话语权的分布呈现出明显的 "金字塔"结构,塔尖由日本、美国及部分欧洲企业构 成,它们在高端光罩制造、核心材料供应及尖端检测设 备领域占据绝对主导地位。

美国的 Photronics 作为全球领先的独立第三方光 罩制造商,在半导体、平板显示等多个领域的光罩制造 方面具有深厚的技术积累。该公司成立于 1969 年,经 过多年的发展,通过持续的研发投入和技术创新,掌握 了一系列先进的光罩制造技术。在光学邻近校正(OPC) 技术方面,Photronics 能够通过精确的算法和先进的 软件工具,对光罩上的图案进行优化,以补偿光刻过程 中的光学畸变,从而提高芯片制造的精度和良率。

日本在光罩产业的优势更为显著,不仅在高端光罩制造企业数量上占据优势,而且在光罩制造的全产业链环节都具备强大的技术实力。除了 Toppan 和 DNP 在高端光罩制造领域的领先地位外,日本企业在光罩基板、光刻胶等关键材料以及光罩制造设备等方面也处于全球领先水平,豪雅(Hoya)和信越化学(Shinetsu)是

全球最大的两家供应商,市场份额合计超过 90%。豪雅生产的光罩基板具有极高的平整度和光学性能,其采用的先进熔炼和加工工艺能够确保基板在不同环境条件下都能保持稳定的性能,为高端光罩的制造提供了坚实的基础。信越化学则在高纯度石英材料的生产方面具有独特的技术优势,其生产的石英基板在杂质含量控制、热稳定性等方面表现出色,广泛应用于 EUV 光罩等高端产品。

在光刻胶方面, JSR、东京应化(TOK)等企业占据了全球半导体光刻胶市场的主要份额。光刻胶作为光罩制造和芯片光刻过程中的关键材料,其性能直接影响到光罩图案的转移精度和芯片制造的质量。日本企业通过长期的研发投入和技术创新,开发出了一系列高性能的光刻胶产品,能够满足不同制程节点的需求。例如,JSR 的 ArF 光刻胶在分辨率、灵敏度和抗刻蚀性能等方面表现优异,被广泛应用于 14nm 及以下先进制程的芯片制造。

长期以来,中国大陆的光罩产业在全球产业链中处于相对弱势地位。在 2020 年以前,国内光罩厂数量虽不少,但整体技术水平较低。以当时知名的 "三兄弟" —— 清溢光电、路维光电和龙图光罩为例,其工艺能力大多集中在 0.25 - 0.5 微米之间;中微掩模电子的能力稍优,可达到 0.13 微米。

近年来,随着国家对半导体产业的高度重视以及产业政策的大力扶持,国产光罩迎来了快速发展的黄金时期。龙图光罩自 2010 年入局半导体掩模版业务,经过多年的技术攻关,将工艺节点从 1µm 提升至 130nm。

2023 年底,**龙图光罩**成功过会,拟募资投向高端半导体芯片掩模版制造基地等项目,加速 130nm 以下制程光罩的国产化进程。该公司在高精度半导体掩模版领域持续进行设备引进与技术攻关,针对半导体掩模版的工艺特点,掌握了图形补偿技术、精准对位标记技术、光刻制程管控技术、曝光精细化控制技术、缺陷修补与异物去除技术等多项自主研发的核心技术,涵盖CAM、光刻、检测三大环节。同时,积极开展技术布局与储备,储备了电子束光刻技术及 PSM 相移掩模版技术,形成了一定的技术成果。目前,龙图光罩已实现130nm 工艺节点半导体掩模版的量产,具备 ±20nm

的 CD 精度和套刻精度,其技术实力和工艺能力在国内第三方半导体掩模版厂商中居于领先地位。其产品已经通过了中芯集成、士兰微、积塔半导体、新唐科技、比亚迪半导体、立昂微、燕东微、粤芯半导体、长飞先进、扬杰科技等多个国内知名晶圆制造厂商的认证。

清溢光电也在不断突破,作为国内规模最大的国产 光掩模供应商之一,该公司在半导体光罩领域持续投入 研发,产品逐步从中低端向中高端迈进。通过与国内科 研机构合作,引进先进人才,清溢光电在光罩制造的关 键技术环节取得了重要进展,如在光罩的缺陷检测与修 复技术方面,开发出了具有自主知识产权的检测算法和 修复工艺,有效提高了光罩产品的质量和良品率。其产 品不仅在国内市场份额稳步提升,还开始涉足国际市场, 与国际大厂展开竞争,产品出口到韩国、日本等半导体 产业发达的国家和地区。

路维光电同样成绩不错,实现了 250nm 制程节点半导体掩膜版量产,掌握 180nm/150nm 节点核心技术,产品广泛应用于多个领域,为国内半导体产业提供了有力支撑。

#### 04 结语

光罩这小小的玻璃片,说到底是场关于"把事做细"的较量。从几百年前用沥青锡版印风景,到现在在纳米尺度画电路,人们总在琢磨怎么把图案做得更准、更小。

那些厉害的国际厂商,无非是把每个细节抠到了极致——基板要平到几乎没有误差,材料要纯到挑不出杂质。这些事,现在国内的厂子也在一步步做,可能还没到最顶尖,但每一步都走得扎实。

龙图光罩实现 130nm 光罩的稳定量产,清溢光电掌握自主的缺陷修复技术,路维光电在成熟领域打磨出可靠工艺,这些都是看得见的进步。无需宏大的叙事,只是把手上的技术做精做透,让下游厂商用得安心顺手。

将来也许没人会特意打听光罩是谁做的,就像现在 没人纠结铅笔是谁造的。但眼下这些一点点磨出来的精 度、攒出来的经验,总会变成底气——证明在这行里, 咱们能把该做的事做好,能跟上趟,甚至慢慢走出自己 的路。

(来源:半导纵横)

## 英伟达披露CPO路线图

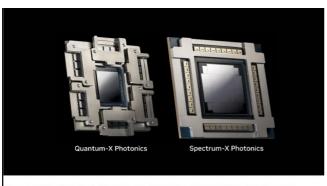

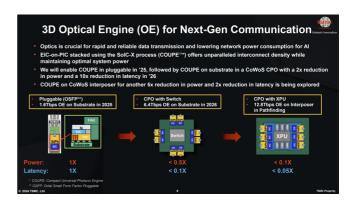

不断增长的 AI GPU 集群之间对通信的极高需求,正推动着人们转向使用光进行跨网络层通信。今年早些时候,Nvidia 宣布其下一代机架级 AI 平台将采用硅光子互连技术与共封装光学器件 (CPO),以实现更高的传输速率和更低的功耗。在今年的 Hot Chips 大会上,Nvidia 发布了有关其下一代 Quantum-X 和Spectrum-X 光子互连解决方案的更多信息,并透露了它们将于 2026 年上市。

Nvidia 的路线图很可能与台积电的 COUPE 路线图 紧密相关,后者分为三个阶段。第一代是用于 OSFP 连接器的光学引擎,可提供 1.6 Tb/s 的数据传输率,同时降低功耗。第二代将采用 CoWoS 封装技术,并采用同封装光学器件,在主板级别实现 6.4 Tb/s 的数据传输率。第三代的目标是在处理器封装内实现 12.8 Tb/s 的数据传输率,并进一步降低功耗和延迟。

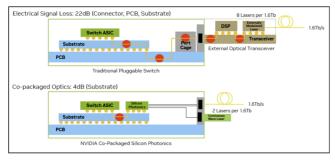

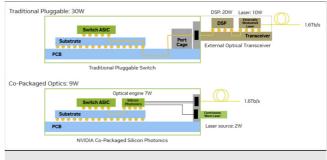

#### 为什么是 CPO?

在大规模 AI 集群中,数千个 GPU 必须像一个系统一样运行,这给这些处理器的互连方式带来了挑战:每个机架不再拥有自己的一级(架顶式)交换机,并通过短铜缆连接,而是将交换机移至机架末端,以便在多个机架之间创建一致、低延迟的结构。这种迁移极大地延长了服务器与其第一个交换机之间的距离,这使得铜缆在 800 Gb/s 这样的速度下变得不切实际,因此几乎每个服务器到交换机以及交换机到交换机的链路都需要光纤连接。

Figure 2. Spectrum-X Photonics delivers 64x better signal integrity

在这种环境下使用可插拔光模块存在明显的局限性:此类设计中的数据信号离开 ASIC,穿过电路板和连接器,然后才转换为光信号。这种方法会产生严重的电损耗,在 200 Gb/s 通道上损耗高达约 22 分贝,这需要使用复杂处理进行补偿,并将每个端口的功耗增加到30W(这又需要额外的冷却并造成潜在的故障点)。据Nvidia 称,随着 AI 部署规模的扩大,这种损耗几乎变得难以承受。

.....

Figure 3. 3.5x power-saving with Spectrum-X Photonics

CPO 通过将光转换引擎与交换机 ASIC 并排嵌入,避免了传统可插拔光模块的缺点,信号无需通过长距离电气线路传输,而是几乎立即耦合到光纤中。因此,电气损耗降低至 4 分贝,每端口功耗降至 9W。这种布局省去了众多可能出现故障的组件,并大大简化了光互连的实施。

Nvidia 声称,通过放弃传统的可插拔收发器,并将光学引擎直接集成到交换机芯片中(得益于台积电的 COUPE 平台),其在效率、可靠性和可扩展性方面实现了显著提升。Nvidia 表示,与可插拔模块相比,CPO 的改进非常显著:功率效率提高了 3.5 倍,信号完整性提高了 64 倍,由于有源设备减少,弹性提高了 10倍,并且由于服务和组装更简单,部署速度提高了约30%。

## 以太网和 InfiniBand 的 CPO

Nvidia 将推出基于 CPO 的光互连平台,适用于以

太网和 InfiniBand 技术。首先,该公司计划在 2026 年 初推出 Quantum-X InfiniBand 交换机。每台交换机将 提供 115 Tb/s 的吞吐量,支持 144 个端口,每个端口的速率为 800 Gb/s。该系统还集成了 ASIC,具有 14.4 TFLOPS 的网络内处理能力,并支持 Nvidia 的第四代可扩展分层聚合缩减协议 (SHARP),以降低集体操作的 延迟。这些交换机将采用液冷散热。

Figure 4: NVIDIA Photonics Switch ASICs with integrated co-packaged silicon photonics engines

与此同时, Nvidia 计划于 2026 年下半年通过 其 Spectrum-X Photonics 平台将 CPO 引入以太网。 该平台将基于 Spectrum-6 ASIC,为两款设备供电: SN6810 提供 102.4 Tb/s 带宽,拥有 128 个 800 Gb/s 端口; SN6800 则可扩展至 409.6 Tb/s,拥有 512 个 800 Gb/s 端口。两款设备也都采用液冷技术。

Nvidia 预计其基于 CPO 的交换机将为日益庞大、日益复杂的生成式 AI 应用提供新的 AI 集群支持。由于使用 CPO,此类集群将减少数千个分立组件,从而实现更快的安装速度、更便捷的维护,并降低每个连接的功耗。因此,使用 Quantum-X InfiniBand 和 Spectrum-X Photonics 的集群在启动时间、首次令牌时间和长期可靠性等指标方面均有显著提升。

Nvidia 强调,共封装光学器件并非可选增强功能,而是未来 AI 数据中心的结构性要求。这意味着该公司将把其光互连技术定位为超越 AMD 等竞争对手的机架级 AI 解决方案的关键优势之一。当然,这也是 AMD 收购 Enosemi 的原因。

#### 未来之路

关于 Nvidia 的硅光子计划,需要注意的一点是, 其发展与台积电 COUPE(紧凑型通用光子引擎)平台 的发展紧密契合。后者预计将在未来几年内不断发展,从而提升 Nvidia 的 CPO 平台。台积电第一代 COUPE 采用该公司的 SoIC-X 封装技术,将 65 纳米电子集成电路(EIC)与光子集成电路(PIC)堆叠在一起。台积电声称,其 SoIC-X 互连具有极低的阻抗,这意味着 COUPE 在功耗方面非常高效。

COUPE 的发展轨迹主要分为三个阶段。台积电的首款硅光产品是一款用于 OSFP(八进制小型可插拔连接器)的光学引擎,其数据传输速率高达 1.6 Tbps,是目前顶级铜缆以太网解决方案最高速率的两倍。这一初始版本不仅承诺提供卓越的带宽,还提升了能效,解决了现代数据中心的两个关键问题。后续几代 COUPE 旨在进一步突破极限。

第二代硅光产品将 COUPE 集成到 CoWoS 封装 (硅基晶圆芯片封装)中,并将光学器件与交换机集成封装。这将实现高达 6.4 Tbps 的主板级光互连。

第三代产品的目标传输速率高达 12.8 Tbps,旨在 集成到处理器封装中。该版本仍处于探索阶段,尚未确 定发布时间表。台积电表示,正在考虑进一步降低功耗 和延迟。

(来源: tomshardware)

## PCIe 8.0正式发布,有望实现256GT/s的AI性能

AI 模型的复杂度每 4 到 6 个月就会翻一番,比摩尔定律还快四倍。受此推动,数据中心基础设施也在快速发展。处理和存储万亿参数模型需要超高速度和低延迟,而当前的超大规模数据中心基础设施则显得力不能及。新的基础设施需要更大的存储容量、增强的计算资源和更快的互连。

PCI 特别兴趣小组 (SIG) 的目标是通过 PCI Express (PCIe) 8.0 实现 256GTransactions/s 的速度,从而为 AI 芯片之间提供更快的链接。

与此同时,通用芯片互连快递 (UCIe) 联盟宣布推出 UCIe 3.0。PCIe 8.0 规范将是 PCIe 7.0 规范数据的两倍,计划于 2028 年发布。

PCI-SIG 技术工作组将开发 PCIe 8.0 规范,其原始比特率为 256.0 GT/s,在 x16 通道配置下双向传输速率高达 1 TB/s。这可能需要新的连接器技术和新技术来降低功耗。

PCI-SIG 总裁兼主席 Al Yanes 表示: "继今年发布 PCIe 7.0 规范后,PCIe 8.0 规范将数据速率翻倍至 256 GT/s,延续我们每三年将带宽翻倍的传统,以支持下一代应用。随着人工智能和其他应用对数据吞吐量的需求不断增长,对高性能的需求依然强劲。PCIe 技术将继续提供经济高效、高带宽、低延迟的 I/O 互连,以满足行业需求。"

| ~Ma<br>35 P | ie to meet needs from handheld/client to server/HPC<br>Total Bandwidth = Max RX bandwidth + Max TX bandwidth<br>mutations yielding 11 unique bandwidth profiles |                 |          |             | 01-      |          |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-------------|----------|----------|----|

| • Enco      | oding overhead and header efficien  Specifications                                                                                                              | cy not included | x2       | Lanes<br>x4 | x8       | x16      | 01 |

|             | 2.5 GT/s (PCle 1.x +)                                                                                                                                           | 500 MB/S        | 1 GB/S   | 2 GB/S      | 4 GB/S   | 8 GB/S   | 17 |

| H           | 5.0 GT/s (PCle 2.x +)                                                                                                                                           | 1 GB/S          | 2 GB/S   | 4 GB/S      | 8 GB/S   | 16 GB/S  | ·  |

| V           | 8.0 GT/s (PCle 3.x +)                                                                                                                                           | 2 GB/S          | 4 GB/S   | 8 GB/S      | 16 GB/S  | 32 GB/S  |    |

| N           | 16.0 GT/s (PCle 4.x +)                                                                                                                                          | 4 GB/S          | 8 GB/S   | 16 GB/S     | 32 GB/S  | 64 GB/S  |    |

|             | 32.0 GT/s (PCle 5.x +)                                                                                                                                          | 8 GB/S          | 16 GB/S  | 32 GB/S     | 64 GB/S  | 128 GB/S | •  |

| М           | 64.0 GT/s (PCle 6.x +)                                                                                                                                          | 16 GB/S         | 32 GB/S  | 64 GB/S     | 128 GB/S |          |    |

| V           | 128.0 GT/s (PCle 7.x +)                                                                                                                                         | 32 GB/S         | 64 GB/S  | 128 GB/S    |          | 512 GB/S | 4- |

|             | 256.0 GT/s (PCle 8.x +)                                                                                                                                         | 64 GB/S         | 128 GB/S | 256 GB/S    | 512 GB/S | 1TB/S    |    |

ABI Research 首席分析师 Reece Hayden 表示: "随着人工智能和其他数据密集型应用的持续快速扩展,PCIe 技术凭借其高带宽、可扩展性和高能效的优势,其需求将长期持续增长。数据中心网络已在为实施PCIe 6.0 技术做准备,并对 PCIe 7.0 规范表现出浓厚兴趣。PCIe 8.0 规范的推出进一步确保了未来业界的带宽需求能够得到良好支持。"

PCIe 8.0 规范旨在支持人工智能 / 机器学习、高速网络、边缘计算和量子计算等新兴应用;以及汽车、超大规模数据中心、高性能计算 (HPC) 和军事 / 航空航天等数据密集型市场。

PCI Express 是通用芯片互连标准 (UCIe) 联盟的关键协议,该联盟还发布了 ICIe 3.0。

封装内芯片间互连的开放标准 3.0 版将数据速率提高了一倍,支持 48 GT/s 和 64 GT/s 的传输,同时进行了增量架构更新,以满足行业对高速、可互操作芯片解决方案日益增长的需求。

UCIe 3.0 规范还引入了一些增强功能,例如运行时 重新校准,通过重用初始化状态在运行期间进行链路调 整来提高功率效率。它还扩展了边带覆盖范围,支持更 灵活的多芯片配置,链路长度可达 100 毫米。

通过映射支持连续传输协议,可在原始模式下实现不间断数据流,适用于 SoC 和 DSP 芯片之间的连接等新应用。

使用标准化管理传输协议 (MTP) 和优先级边带数据包进行早期固件下载可提高系统响应能力和可靠性,这是可选的可管理性功能,设计人员如果选择针对时间敏感的系统事件进行确定性、低延迟信号传输,则可以实现这些功能。

UCIe 联盟主席兼三星电机公司副总裁 Cheolmin Park 表示: "UCIe 3.0 代表着 chiplet 行业向前迈出的关键一步,它提供了扩展多芯片设计所需的速度、效率和可管理性。凭借更高的数据速率和更强大的可管理性,

下一代 UCIe 技术将赋能开发人员构建更灵活、可互操作且高性能的 SiP 解决方案,我们将携手构建一个真正开放且可互操作的 chiplet 生态系统。"

具体而言,PCIe 技术在以下领域展现出巨大的应用潜力:

·云计算:占据最大市场份额(超 50%),在数据中心和服务器领域将继续主导应用。

·汽车: 随着 AI 和高级驾驶辅助系统 (ADAS) 的发展, 汽车市场对 PCIe 的需求逐渐上升。

·移动设备和消费电子市场也占据了稳定份额,预 计将不断扩大。

随着 AI、HPC 及大数据的逐步深入,PCle 技术将继续在各行各业中发挥重要作用。这种广泛采用的芯片

间互联协议不仅提升了设备的互操作性,也促进了 AI 技术的快速普及和应用。

PCIe 通过 PAM4、FEC 技术和低功耗模式等多项创新,能够为大型生成式 AI 模型提供支持,其核心优势在于高带宽和低延迟。为此,数据中心中的 AI 芯片供应商纷纷选择 PCIe 卡格式的产品,以满足不断增长的互连需求。

(来源:半导体产业纵横)

## 全国各地集成电路扶持政策

集成电路资金补贴:萧山重庆最"大方"

当前,各省市针对集成电路产业多个环节推出高额资金补贴,助力项目落地。

2025 海淀区经济社会高质量发展大会上发布《中关村科学城集成电路流片补贴申报指南》

2月14日,北京海淀区在2025海淀区经济社会高质量发展大会上正式发布《中关村科学城集成电路流片补贴申报指南》。《申报指南》中明确,面向海淀区从事集成电路设计业务的企业,支持集成电路设计企业开展多项目晶圆或工程产品首轮流片(全掩膜),单个企业补贴最高1500万元,在支持集成电路设计企业开展工程产品首轮流片(全掩膜)方面,对境内开展先进制程(14nm及以下)工程产品首轮流片(全掩膜)的企业,按照不超过产品流片费用的30%予以奖励,单个企业上限800万元;对在境内开展成熟制程(14nm以上)工程产品首轮流片(全掩膜)的企业,按照不超过产品流片费用的20%予以奖励,单个企业上限500万元;对在境外开展先进制程(14nm及以下)工程产品首轮流片(全掩膜)的企业,按照不超过产品流片费用的20%予以奖励,单个企业上限500万元;对在境外开展先进制程(14nm及以下)工程产品首轮流片(全掩膜)的企业,按照不超过产品流片费用的15%予以奖励,单个企业上限500万元。

4月30日,重庆高新区发布《重庆高新区促进集成电路产业高质量发展的若干措施》。该《措施》共计19条,单项最高奖励可达5000万元。其中,13条措施专门针对设计端、封测模组端企业精准施策。例如,对设计企业流片给予最高3000万元奖励;鼓励企业加大投入,最高奖励5000万元,鼓励企业融资,最高奖励3000万元;助力企业做大做强,最高奖励1500万元;在场地保障方面,最高奖励1000万元。

5月27日,浙江省杭州市萧山区人民政府发布《关于促进集成电路产业高质量发展的若干政策》中也提到,为构建产业链协同发展,将加大重大项目培育,对符合集成电路制造、封测、装备、材料类产业导向的重大项目,根据其技术产品、工艺水平和市场前景等,经评审,最高按照研发投入的30%(包括流片费用、IP购买费用、

租用或购买 EDA 工具费用等)、设备投入的 20% 予以补助,最高 1 亿元;对符合条件的集成电路设计企业,加大关键材料、核心设备和 EDA 工具的支持。对集成电路关键材料、核心设备等自主研发投入 5000 万元以上并实现实际销售的,按照不超过其研发投入的 15%给予补助,最高补助 5000 万元。对开展 EDA 工具技术攻关,自主研发投入 1000 万元以上并实现实际销售的企业,经评审,按照不超过其年度自主研发投入的 15%给予补助,最高补助 2000 万元;集成电路设计企业对重点支持领域的芯片产品开展流片,首次流片费用 1000 万元以上的,经评审,按照不超过其流片费用的 15%给予补助,其中,对工艺制程大于 28nm 的,年度补助总额最高 300 万元;对工艺制程小于等于 28nm 的,年度补助总额最高 1000 万元。单家企业年度补助总额最高 2000 万元。

6月16日,广州开发区经济和信息化局、广州市 黄埔区工业和信息化局联合印发《广州开发区黄埔区 支持集成电路产业高质量发展若干政策措施》。对使用 多项目晶圆(MPW)流片进行研发或首次完成全掩膜 (Fullmask)工程流片的设计企业,以及开展高端传 感器首轮流片的智能传感器企业,按不高于流片费用 40%分档补助,每家企业每年最高500万元;重点围 绕集成电路制造关键部件和系统集成开展持续研发和技 术攻关,对于新引进的固定资产投资1000万元以上且 实现小升规的产业化项目,按不超过设备和工器具投资 额15%分档扶持,最高1000万元。

7月30日,深圳市科技创新局发布《2025年度重点产业研发计划(第一批)项目申请指南》,将半导体与集成电路列为重点支持领域之一。该计划采取"揭榜挂帅"方式,对战略性新兴产业和未来产业关键核心技术攻关予以支持,提升深圳市科技攻关体系化能力。资助项目总数不超过3000个,单个项目资助强度最高不超过3000万元。

8月5日,上海市科学技术委员会发布《2025年度基础研究计划"集成电路"(第二批)项目申报指南》,针对集成电路领域的前沿技术研究,如集成电路设计、制造工艺、材料等基础研究方向提供资金支持,项目执行周期为2025年10月至2027年9月,单个项目最高

资助 100 万元。并且,上海各区政府纷纷出台针对性政策。浦东新区在 2025 年 2 月和 7 月分别发布了 2025 年度促进集成电路和新一代通信产业高质量发展专项的第一批和第二批的申报通知,针对 IP 购买、首轮流片、多项目晶圆(MPW)项目等提供资金支持,并对获得市级专项资金的项目给予配套奖励,强化产业链协同;临港新片区于 2024 年 10 月修订《集聚发展集成电路产业若干措施》,支持集成电路装备、材料、制造、封测等领域自主研发取得重大突破、带动产业集聚的引领性项目。按照项目新增投资的 10% 比例给予支持,支持金额不超过 1 亿元。对于集成电路产业生态链带动发挥重大作用的项目支持金额不超过 10 亿元;对于集成电路关键环节的突破"卡脖子"技术重大项目支持比例不超过项目新增投资的 30%。

#### 健全产业生态: 各地各显身手

经过近几年的迅速发展,我国已经有一定数量的集成电路企业,但是规模、能力仍有待提升,今年各省市的多种政策手段,着力在健全产业生态,推动产业长期健康发展。

#### 广州开发区经济和信息化局 广州市黄埔区工业和信息化局关于印发广州开发 区 黄埔区支持集成电路产业高质量发展若干政策措施的通知

現开投信規定(2023)4号 作用开发区受済和信息化局 广州市資補区工金和信息化局关于印发广州开发区 黄埔区支持靠城电路产业高质量发展若干政策措施的通知 区首有关单位: 《广州开发区 黄埔区支持集成电路产业高质量发展若干政策措施》全经广州开发区管竞会、黄埔区政府同意、現印发实施。执行过程中知遇问题,通径 回区工业印息经用展展。

广州开发区经济和信息化局 广州市黄埔区工业和信息化局 2025年6月16日

在技术创新扶持方面,《广州开发区黄埔区支持集成电路产业高质量发展若干政策措施》中提出,在提升高端芯片设计能力上,重点突破 CPU、GPU、FPGA 等高端芯片设计,大力支持人工智能芯片、光芯片、物联网芯片、存储芯片、射频芯片、基带芯片、车规级芯片、显示驱动芯片等芯片的开发设计,鼓励企业自主开展基于新器件、新材料、新工艺的 RISC-V、ARM 等高端芯片架构设计;深圳市发展和改革委员会在7月出台的《深圳市关于促进半导体与集成电路产业高质量发展的若干

措施》以"强链、稳链、补链"核心目标,从高端芯片产品突破、加强芯片设计流片支持、加快 EDA 工具推广应用、突破核心设备及配套零部件、突破关键制造封装材料、提升高端封装测试水平、加速化合物半导体成熟等方面,提出了 10 条具体支持举措,推进全市半导体与集成电路产业重点突破和整体提升。

在产业协同方面,中共广东省委办公厅、广东省人 民政府办公厅印发《广东省建设现代化产业体系 2025 年行动计划》,提出加快华润微、方正微、粤芯、增芯 等重大项目建设和产能"爬坡",补齐集成电路制造、 先进封测等短板,大力发展材料及装备产业,谋划建设 光芯片产业创新平台。通过这些重大项目的推进,促进 产业链上下游企业的协同合作,形成产业集群效应,提 高产业整体的生产效率和创新能力。

《广州开发区黄埔区支持集成电路产业高质量发展若干政策措施》中提出,要优化产业发展布局,支持重点项目加快落地,推动优势资源和优质企业向符合产业布局要求的园区集聚,在芯片设计、特色工艺、先进封装测试、EDA工具、装备及零部件等领域实现突破,打造涵盖设计、制造、材料、装备与零部件、封测等环节的全产业链,建设综合性集成电路产业聚集区。通过政策引导,促进产业集聚,加强企业间的合作与交流,实现资源共享和优势互补,进一步提升产业协同发展水平。

杭州市萧山区人民政府发布《关于促进集成电路产业高质量发展的若干政策》中提到,为支持"芯机联动",鼓励终端厂商、系统集成商试用非关联集成电路企业自主研发、首次上市的设备、材料、芯片或模组。对使用非关联集成电路企业的首次上市产品,且当年度采购金额累计达 1000 万元以上的企业,按当年使用金额分档给予奖励。而对提供 EDA 工具和 IP 核、设计解决方案、先进工艺流片、先进封测服务、测试验证等设备,用于高端芯片支撑服务的集成电路公共技术平台,完工后实际建设投入在1亿元以上的,经评审,按其投资额的6%给予补助,最高 1000 万元。

《重庆高新区促进集成电路产业高质量发展的若干措施》中有3条措施分别用于支持公共服务平台(包含硅光 EPDA 平台)建设以及车规级产品认证。其中,对公共服务平台建设最高奖励3000万元;设备、材料

验证最高奖励 500 万元; 车规级产品认证最高奖励 300 万元; 还有 3 条措施分别支持供应链协同、高端人才引育及产业氛围营造。如鼓励供应链协同,最高奖励 1000 万元; 鼓励企业招引行业高端人才及团队,最高给予 500 万元奖励; 鼓励企业举办行业活动,最高奖励 600 万元。

在企业整合方面,2024年12月,上海市政府办公厅发布《上海市支持上市公司并购重组行动方案(2025-2027年)》,提出设立100亿元集成电路设计产业并购基金,支持集成电路企业通过并购整合产业链资源。目标到2027年,在集成电路等重点产业领域培育10家左右具有国际竞争力的上市公司,形成3000亿元并购交易规模,激活总资产超2万亿元。

在税收优惠方面,3月27日,国家发展改革委等部门发布了《关于做好2025年享受税收优惠政策的集成电路企业或项目、软件企业清单制定工作的通知》,其中,明确了享受税收优惠政策的集成电路企业或项目、

软件企业清单制定工作事项,各地严格按照国家政策要求,推动符合条件的集成电路企业享受税收优惠。北京积极响应国家政策,推动符合条件的集成电路企业享受企业所得税减免、研发费用加计扣除等政策,鼓励企业加大研发投入与扩大生产规模。通过这些税收优惠政策,企业能够节省大量资金,将更多资源投入到技术研发和生产扩张中,提升企业的创新能力和市场竞争力;4月,江苏省财政厅发布的《关于享受集成电路和软件产业企业所得税优惠政策有关事项的通知》中明确,集成电路和软件产业企业根据企业类型分别适用清单管理方式和转请核查方式来享受企业所得税优惠,进一步细化税收优惠落实流程。

随着各省市集成电路政策的持续推进和落实,我国 集成电路产业有望迎来更加蓬勃的发展。产业规模将不 断扩大,技术水平将显著提升,产业链将更加完善,产 业生态将更加优化。

态将更加优化。

(来源:中国电子报)

## 浙江省委办公厅省政府办公厅印发《关于全面推进科技 创新和产业创新深度融合的实施意见》的通知

为深入贯彻习近平总书记考察浙江重要讲话精神,加快建设创新浙江、因地制宜发展新质生产力,现就全面推进科技创新和产业创新深度融合提出如下实施意见。

#### 一、强化以"两个显著"为方向的目标体系建设,打造新质生产力竞争高地

紧扣产业结构显著优化和经济发展质效显著提升目标,制定年度工作任务书和改革清单,明确路径、压茬推进。到 2027 年,科技创新和产业创新深度融合浙江路径取得重大突破,推动科技创新更强、产业能级更高、创新主体更活、创新生态更好,制造业增加值占 GDP 比重保持基本稳定,浙江特色现代化产业体系竞争力明显增强。到 2030 年,科技创新和产业创新深度融合浙江路径更加成熟完善,基本建成全球先进制造业基地,浙江特色现代化产业体系全面形成。到 2035 年,科技创新和产业创新深度融合浙江路径全面形成,建成全球先进制造业基地,浙江特色现代化产业体系更具国际竞争力和全球影响力。

#### 二、强化以企业为主体的创新组织体系建设,打造创新企业集聚高地

- (一) 深化企业主导的产学研用合作。强化企业科技创新主体地位,支持企业全面参与技术创新决策、科研组织和成果转化,鼓励企业设立研发准备金。对标国际先进,扩面提质企业研发机构,支持校院企共建互建。建立"高校+平台+企业+产业链"的结对合作机制,鼓励和引导高校、科研院所按照"先使用后付费"方式把科技成果许可给企业使用。

- (二)深化大中小企业融通创新。培育壮大科技领军企业,支持企业牵头组建创新联合体,构建与重大科技计划联动实施机制。实施大中小企业融通创新"携手行动",支持中小企业针对大企业配套需求开展技术攻关。支持平台企业开展科技创新、模式创新、应用场景创新。

- **(三)快速扩大科技型中小企业规模数量。**深化"小升规"培育行动,加强支持科技型中小企业融资,加快初创型项目产业化,推动科技型中小企业扩大规模、快速发展。

- (四)大力培育高新技术企业和专精特新企业。完善高新技术企业培育机制,健全专精特新企业培育体系,实施专精特新中小企业"四提一强"等行动,制定独角兽企业培育措施,加快孵化、挖掘、引进独角兽企业,加快培育瞪羚企业。实施"雄鹰行动""凤凰行动",建设世界一流企业。

#### 三、强化以产业为主场的创新人才体系建设,打造企业人才汇聚高地

- (五)加强科技型企业家引育。实施科技型企业家选育计划,完善"新知新质圆桌会"合作平台,打造"科学家+企业家"创新联合体。支持地方实施"人才+项目"一体化运作机制。支持高校院所科研人员创新创业,鼓励其按规定到企业兼职。

- (六)有序推进企业"薪火"传承。实施"浙商青蓝接力工程"、新生代企业家"双传承"计划、"浙农英才" 计划。开展企业管理现代化对标提升工程,加大职业经理人、创新管理师培养力度。

- (七)全面加强校院企人才共育共享。探索实施校院企人才有序流动"互聘共享"计划,推广"产业教授""科技副总"机制,开展"百名博导带团队进企业研究院、百家企业研究院带项目进高校"活动。建立完善"企业认定、政府认账"机制,支持符合条件的企业开展人才计划自主评审。深化现代产业学院建设,实施卓越工程师培养工程。

#### 四、强化以市场为导向的供给转化体系建设,打造创新成果转化高地

- (八) 进一步加强关键核心技术供给。实施省重大科技、基础研究、重点行业领域科技等计划和省地协同项目。完善企业主导的需求凝练和组织实施机制,深化研发攻关,每年实施一批制造业领域重大科技项目,加快形成一批"1到10""10到100"的标志性成果。

- (九)进一步加强产业共性技术供给。实施产业基础再造工程,完善首台(套)产品工程化攻关和推广应用全流程服务机制。实施"人工智能+"行动,推进人工智能技术在重点集群应用,大力推广数字化改造解决方案和先进节能低碳工艺技术装备。

- (十)进一步加强创新成果转化应用。构建创新成果有效供给和高效转化机制,面向全球招引创新成果,面向全省精准落地创新成果。实施"企业出题、政府助题、平台答题、车间验题、市场评价"协同攻关机制改革,畅通"平台引人才、人才带技术、技术变项目、项目融资金、实现产业化"的创新发展之路。推进中小企业知识产权战略推进工程、专利导航工程,建设知识产权交易中心、运营中心,实施高价值专利培育项目。

- **(十一)大力发展科技服务业**。加强科技服务体系建设,提升网上技术市场、技术转化中心等能级,常态开展创新产品遴选推广活动。培育专业化技术经理人。

#### 五、强化以赋能为特色的创新平台体系建设,打造技术集成应用高地

- (十二)加快培育高水平中试平台。省级主导、省市联动建设制造业中试平台,推广"中试+投资+孵化"运营模式,鼓励地方制定支持政策。鼓励地方按照先培育、后认定方式,支持概念验证中心建设。

- (十三)加快建设高质量孵化器加速器。实施分类管理,支持企业、高校院所、投资机构等新建孵化器,提能升级现有孵化器,鼓励地方对成效突出的给予支持。构建梯度接续孵化培育体系,提供全生命周期优质服务。

- (十四)大力建设高能级产业平台。推动高新区重塑重构、经开区提能升级。加快高新区高质量发展,全面优化布局,推动国家高新区争先进位、省级高新区做专做精。推动自贸试验区、"万亩千亿"新产业平台等提质增效,培育海洋产业平台。

#### 六、强化以创新为动力的先进集群体系建设,打造现代产业发展高地

- (十五)推进"415X"集群提能升级。实施"415X"先进制造业集群培育工程,构建"省级—国家级—世界级"集群梯度培育体系。强化"链长+链主"制,优化"核心区+协同区"培育机制。奋力推动信息技术服务、生物医药、新型功能材料、数字安防、现代纺织服装、工业母机等集群向世界级集群迈进。

- (十六)推进传统产业升级焕新。持续实施"腾笼换鸟、凤凰涅槃"攻坚行动,利用数字技术、绿色技术改造提升石油化工、家具家电等传统产业,推动历史经典产业传承创新发展。实施"千亿技术改造和设备更新工程"。支持优势企业内生裂变。实施质量提升强企行动,鼓励企业参与标准制修订,构建"浙江制造"品牌矩阵。实施农业"双强"、"耕海牧渔丰收"等行动,推广现代化交通产业集群发展模式,促进建筑业、海洋产业高质量发展。

- (十七)推进新兴产业培育壮大。深化国家数字经济创新发展试验区建设,支持做强人工智能、集成电路等省级产业集群,推动智能物联、高端软件、智能光伏等打造具有国际竞争力的数字产业集群。"一业一策"培育新能源、新材料、基础软件等战略性新兴产业集群,深化高端装备、新能源汽车、航空航天、综合交通等优势产业集群建设。

- (十八)推进未来产业前瞻布局。建立前沿技术预见机制,滚动编制未来产业领域指南。建立未来产业投入增长机制,聚焦人形机器人、脑机接口、量子技术、合成生物、低空经济、工业软件、前沿新材料、空天深海深地等领域,建设未来产业先导区。

#### 七、强化以一流服务为优势的创新生态体系建设,打造创新要素配置高地

**(十九)强化财政资金支持。**发挥省级专项资金带动作用,深化财政科研经费包干使用机制。落实政府采购创新产品支持政策。探索降低制造业综合成本。

- (二十)强化金融资本支持。依托科创金融改革试验区,深化科技金融体制创新。更好发挥"4+1"专项基金、省属企业投资基金引导作用,动态扩大科创母基金规模,探索建立并购基金,推动设立 S 基金并开展市场化运作。落实央行再贷款、再贴现等政策工具支持。支持创投机构健康发展,畅通投资退出机制,引导资本投早、投小、投长期、投硬科技。

- (二十一)强化创新基础设施共建共享。实施新型算力体系支撑工程,开展"算力普惠"行动,推进"智能券"政策服务。大力培育国际一流通用大模型和开源社区。推动重大科技基础设施、大型科研仪器设备等向企业开放。积极探索数据价值增值化新路径新模式。

- (二十二)强**化应用场景先行先试**。发布科技创新和产业创新深度融合应用场景建设需求清单。积极支持人工智能、人形机器人、智能网联汽车、智慧绿色交通、低空经济等领域场景建设。

- (二十三)强**化改革先行先试**。尊重基层首创精神,鼓励地方聚焦关键环节、堵点难点积极创新探索,加强典型案例征集推广。探索包容审慎监管方式。

- (二十四)强化工作机制保障。建立工作例会等机制,项目化、清单化、时限化推动落实。根据加快建设创新浙江、 因地制宜发展新质生产力绩效评价体系,开展指导服务,强化结果运用。

# 浙江省科学技术厅关于组织申报2026年度省"尖兵""领雁"科技计划科技合作项目的通知

各设区市科技局,各有关单位:

为加快建设创新浙江、因地制宜发展新质生产力,聚焦"315"科技创新体系,加强全方位、多层次、宽领域的国内外科技合作交流,构建具有全球竞争力的科技创新开放环境,按照 2026 年度省"尖兵""领雁"科技计划项目申报工作总体部署,决定启动科技合作项目申报,现将有关事项通知如下。

一、项目总体定位

2026 年度省 "尖兵" "领雁"科技计划科技合作项目总体分为国际(含港澳台)科技合作项目、对口支援与东西部协作项目两大类。根据任务性质,采用公开竞争和择优委托相结合的遴选方式。

- **(一) 国际(含港澳台)科技合作项目。**围绕服务科技外交、构建合作网络、支撑合作载体等重点任务,部署重点国家(地区)和关键领域合作项目。

- **(二)对口支援与东西部协作项目。**围绕服务区域协调发展,聚焦对口地区经济社会发展重大需求,开展跨省域应用研究和先进适宜技术推广示范。

- 二、申报推荐要求

#### (一) 申报要求

1. 申报主体应整合优势创新团队,充分利用国际、港澳台地区、对口地区等优势力量,开展联合攻关与技术示

范推广。

- 2. 申报单位原则上应建有纳入"白名单"的国家级、部级、省级、部门科技创新平台基地,平台基地应与申报 项目领域相关,项目负责人应同时为平台基地成员。"政府间科技合作项目"除外。

- 3. 同一科研人员作为项目负责人的,同年度只能申报 1 项省科技计划项目,且科技合作项目不得与同年度省自 然科学基金项目同时申请。

- 4. 申请人应如实填写申请材料,如发现弄虚作假、故意重复申请等科研诚信问题,依据有关规定严肃处理,记 入浙江省科研诚信档案。经组织开展申请书相似度审查,对相似度30%以上(含)的,按形式审查不通过处理, 存在科研失信行为的根据有关规定予以处理。

- 5. 国际(含港澳台)科技合作项目须附上合作协议,合作双方事先对知识产权归属和产品或工艺的商业化达成 共识,具有明确的分工。对口支援与东西部协作项目须由帮扶地市级及以上指挥部(工作队)出具推荐函,牵头单 位可按合同约定拨付不超过财政补助经费的 50% 至帮扶地合作方。

- 6. 申报单位、限项申报、资金、科研诚信和科研伦理等要求及其他注意事项,详见《浙江省科学技术厅关于组 织申报 2026 年度省"尖兵""领雁"科技计划项目的通知》。

#### (二) 推荐要求

实行申报限额与择优推荐相结合的方式,"政府间科技合作项目"不设推荐限额,其他项目推荐数可登录申报 系统查询。推荐单位应严格对照目标任务、申报条件等要求择优推荐,并出具推荐承诺函。

三、申报方式和时间安排

- (一) 网上填报。请各申报单位使用政务服务网账号,登录浙江省科技管理平台(https://pm.kjt.zj.gov. cn) ,点击"科技计划-其他-科技合作项目-申报"进行网上填报。**网上填报受理时间:2025 年 8 月 28 日至 9** 月22日17:30。

- (二) 审核推荐。请推荐单位做好组织申报和审核推荐工作,严格履行主体责任,加强审核把关,并于9月26 日 17:30 前将推荐函和推荐汇总表、承诺书盖章后扫描上传至申报系统。

#### (三)咨询方式

联系人: 0571-87054742 (项目中心) 0571-87054015 (合作处 - 国际合作) 0571-87054066 (合作处 - 对口帮扶)

0571-85118011(技术支持)

附件: 2026 年度省"尖兵""领雁"科技计划科技合作项目申报指南

浙江省科学技术厅 2025年8月21日

## 杭州市上城区人民政府办公室关于印发《上城区支持人 工智能产业创新发展若干政策措施》的通知

根据《浙江省人民政府印发〈关于支持人工智能创新发展若干措施〉的通知》及《杭州市人民政府关于印发〈杭州市加快建设人工智能创新高地实施方案(2025 年版)〉的通知》文件精神,结合我区实际,为抢抓省市一体推进人工智能高质量发展机遇,塑造上城区人工智能创新发展特色优势,特制定《上城区支持人工智能产业创新发展若干政策措施》,具体举措如下:

#### 一、支持对象

围绕人工智能产业,重点引进和培育模型、算力、数据、智能终端等细分领域相关企业,并给予相应扶持。

- 二、支持政策

- **1. 降低算力成本**。支持采购智能算力服务和模型服务的用户企业申请杭州市"算力券",对符合市级政策的,按照市级认定补贴金额给予 100% 额外补助,单家企业最高 500 万元 / 年。(责任单位:区发改经信局)

- **2. 支持模型研发**。支持企业开展多模态大模型研发并申请市级模型研发补助。对入选市级优秀专用模型的牵头研发单位,按照市级认定的补助金额给予最高 100 万元的额外补助。对获得中央网信办生成式人工智能模型备案的企业,按照市级认定的奖励金额给予最高 20 万元的额外奖励。(责任单位:区发改经信局、区委网信办)

- 3. 强化数据支撑。支持企业和机构通过杭州数据开放平台向社会提供训练、验证、测试、语料等数据集,对入选市级优秀高质量多模态开放数据集的,按照市级奖励金额给予最高 50 万元额外奖励。对通过数据交易平台或可信数据空间购买非关联方语料进行大模型研发和应用的企业,按照不超过合同金额的 30% 给予补助,单家企业每年最高补助 200 万元。对入选国家、省、市可信数据空间试点示范的项目,按照实际获得的补助金额给予最高 100 万元额外补助。鼓励和支持企业借助公共数据授权运营、"数据要素 ×"大赛等开放平台,运用公共数据开展人工智能相关场景的研发。(责任单位:区数据资源局、区发改经信局)

- **4. 鼓励技术攻关**。支持人工智能企业以关键技术突破和产业链条延伸为重点开展科技研发攻关,承担国家、省、市重点科研任务和重大科研项目。鼓励人工智能企业加大研发投入,对于成长性较好的,经认定,按照不超过其研发投入增量的 30% 给予奖励,单家企业最高 3000 万元。(责任单位:区科技局)

- **5.建设创新载体**。支持人工智能企业打造创新联合体、企业研究院、重点实验室、概念验证中心、成果转化基地、中试基地等创新载体,分别给予最高 50 万元、150 万元、300 万元、550 万元、1000 万元、2200 万元奖励。支持省级以上实验室、技术创新中心等高能级科创平台创建,最高补助 3000 万元。支持人工智能企业与高校、科研院所、科研重器开展技术开发、技术服务等,经认定,按合同金额一定比例予以补助,单个企业最高补助 100 万元。(责任单位:区科技局)

- **6. 给予创业补助**。鼓励人工智能企业创业发展,经认定,给予最高 20 万元一次性创业补助;对获得国家、省科技进步奖,入选重量级行业榜单,获得亿元以上投资,取得"单项冠军"等资质,或在国内外有影响力相关大赛获奖的,经认定,最高给予 200 万元一次性创业补助。(牵头单位:区科技局、区发改经信局、玉皇山南基金小镇管委会)

- **7. 支持企业成长。**支持"新势力"企业发展,按规定给予相关奖励支持。培育"领军型"企业梯队,对首次认

定的制造业单项冠军企业、专精特新"小巨人"企业、"隐形冠军"企业,分别给予不超过 200 万元、150 万元、150 万元的奖励。鼓励企业发展,对经认定,发展势头强劲的优质企业,给予最高 5000 万元奖励。(责任单位:区发改经信局)

- **8. 提供场地支持**。支持上城区科创空间和环国家大学科技园创新生态圈发展。对新设立的人工智能企业,符合条件的,经认定,给予最高 1000 平方米办公场地三年免租。(牵头单位:区科技局、钱塘智慧城管委会)

- **9. 建设特色平台**。支持优质企业向产业楼宇、产业园集聚。经认定的区级人工智能特色楼宇产业园,分档给予 200 万元、100 万元、50 万元奖励。对入选市级人工智能标杆产业园和产业生态创新空间的,在市级运营经费补助 的基础上,给予最高 100 万元的额外补助。(责任单位:区发改经信局)

- **10. 支持场景示范**。支持事业单位、国企、各行业企业开放应用场景,与人工智能企业共建"人工智能+"创新应用。每年择优评选不超过 10 个区级示范项目给予供需双向支持,按照项目总投入的 30%,给予最高 300 万元补助;对入选省、市"人工智能+"标杆型示范项目的,按照省、市级补助金额给予最高 100 万元的额外补助。对在上城区举办具有重大影响力的人工智能产业领域峰会、论坛、展会、大赛等活动的单位,经认定,按最高不超过审定支出的 50%,单家企业最高补贴 100 万元 / 年。(责任单位:区发改经信局、区科技局)

- **11. 加大人才引育**。经我区自主培育的人工智能领域海内外领军人才,最高给予 600 万元安家补助。鼓励人工智能企业培育数字服务业人才,在认定时给予一定名额倾斜。人工智能领域博士后出站 1 年内留上城(来上城),最高给予 100 万元安家补助。企业引进人工智能领域领军人才的,给予最高 80 万元引才资助。对来上城就业的人工智能相关专业的优秀应届大学生,给予最高 15 万元生活补贴。(责任单位:区委人才办、区科技局、区人力社保局)

- 12. 强化金融保障。加强产业基金资金扶持,充分发挥区级产业基金引导和撬动社会资本的杠杆作用,通过产业基金股权直投、母子基金合作方式投向人工智能关联方向的基金规模不低于 100 亿元。支持企业上市融资,将人工智能重点企业纳入上市重点培育企业名单,组织开展上市专题培训。支持人工智能优质企业运用债券融资支持工具,发行科技创新公司债券,通过信用风险缓释凭证、担保增信等方式,支持企业在银行间债券市场发行科创票据。(责任单位:上城资本、玉皇山南基金小镇管委会)

#### 三、附则

- 1. 扶持资金由区财政局统筹平衡。同一项目按"从优、从高、不重复"和进档差额原则进行补助。上级已有补助的,本文件补助含区级配套资金,其中涉及额外补助的,由区级承担。如遇上级政策调整的,以调整为准。

- 2. 当年发生违法犯罪和出现安全生产、环境污染等较大责任事故的企业,不能享受扶持政策。扶持对象均须对申请材料的真实性负责,并承担相应法律责任。

- 3. 本文件自 2025 年 9 月 17 日起施行,试行期一年。

# 中国工程院院士倪光南:构建脑、眼、行动协同的系统,提高机器人智能水平

8月10日,中国工程院院士倪光南在2025世界机器人大会主论坛上进行了题为《"AI+空间计算"让机器看懂世界》的主旨演讲。他表示,当前人工智能引领科技范式变革,在"人工智能+"行动的背景下,要提高机器人智能水平,以"AI+机器人"更好地发挥机器人新质生产力的作用。

倪光南表示,"AI+空间计算"开启了二维交互向三维交互发展的新范式。"AI+空间计算"是当前落实"人工智能+"行动的一项关键核心技术。空间计算作为一种全新的计算方式,它

是物理世界和数字世界之间的桥梁,正在重塑人类、机器和世界的交互方式,是推动机器人技术落地的关键核心技术之一。

倪光南表示,目前来看,生成式大语言模型引领着科技的发展,但是大语言模型学习到的内容不是物理世界的全部,生成式 AI 并不能完全辐射复杂的物理世界。空间计算和 AI 的融合正以一种全新的方式重构三维物理世界,拓展了大模型通向物理世界的桥梁,促进了物理世界和数字世界的融合。

他引用图灵奖获得者杨立昆教授的理论,"一个大模型学习的信息量大概是 10 的 14 次方",相当于互联网上所有公开文本信息量的总和,换算过来,人类几十万年才能学到这些信息量。但是,一个 4 岁的小孩睁开眼睛能学到的信息量也大概是 10 的 14 次方,这说明当前的大语言模型训练所用的文本信息是不够的。

"我们要认识世界、理解世界还需要用到大量的视频信息。"倪光南说,"视觉是智能的起点,是物理世界控制感知的基础,是大脑和物理世界作用的桥梁。因此,我们要重视'眼睛'的作用。"

以机器人在工厂工作的实际案例,机器人"看到"的世界和人眼看到的大体相当,机器人的视觉可以通过"AI+空间计算"对看到的事物进行理解和建模。"过去,数字世界和物理世界相当于影射的关系,现在要把数字世界和物理世界融合起来。"倪光南说。

"总的来说,我们希望人、货、机将来在工厂生产线上协同工作、取长补短。"倪光南说。

谈到机器人,从过去作为自动化的工具变成如今智能化的主体,倪光南表示,机器人现在是由具身智能系统进行控制。我国机器人产业发展潜力巨大,面对机器人产业万亿级的规模,倪光南表示,我们要通过提高机器人的智能水平,发挥它作为新质生产力的作用。

倪光南详细介绍了机器人如何实现智能。他表示,机器人的智能一般由三大部分组成:即脑、眼、行动系统, 共同组成具身智能系统。"但目前,我们在机器人的'脑'和'眼'的方面投入还不够,存在短板,需要加大这方 面的投入,更好地体现机器人的效能。"倪光南强调。

他以汽车智驾为例,汽车智驾分为 L1~L5 不同的等级,机器人同理。目前的机器人一般是 L1~L3 阶段,"我们希望通过'眼'和'脑'的发展,把机器人整体的智能水平发展到 L4 以上,这样机器人才能真正体现出它移动、自主、高精度的能力,真正发挥出机器人在提升生产效率方面的作用。"今后的机器人不仅是一个操作系统,而是包含"大脑""眼睛""行动协同"的具身智能体。在这样系统的支撑下,工业自动化机器人才能进一步发展到现在的人工智能时代"AI+机器人",发挥更大的效能作用。

倪光南强调,要达到这个要求,关键在于提升机器人的智能水平。"我们要用'脑—眼—行动'协同的系统来提高机器人的智能水平,真正让机器人能够看见世界、理解世界、行动于世界。"倪光南说。

但机器人要从自动化的工具发展为"AI+机器人",要经历复杂的过程。首先,机器人必须基于大模型拥有自己的"大脑"。其次,机器人的智能系统应该突出"眼睛"的作用。"AI+空间计算"的解决方案,是用普通的单目摄像头+神经网络学习的方式,让机器人具备类似人类的视觉,且具备很好的适应性。最后,机器人要和很多本体发生交互,因此需要一个操作系统。倪光南建议使用开源的 AGIROS 支撑"机器人的行动",全面推动智能机器人领域的发展。

(来源:中国工信新闻网)

## 清华大学汪玉教授: 当AI重塑产业,新时代的育人思考

#### 01 产业变革:如何实现从并跑转变为领跑

中国电子信息产业的发展,就像一条蜿蜒向前的长河。

中国电子信息产业的建设可以追溯到新中国成立初期。以清华大学电子工程系为例,其前身为 1952 年从电机系分离出的无线电专业,这是中国系统培养电子工程人才的起点。此后,清华大学在晶体管制造、雷达研发等相关领域持续深耕。

回顾中国电子信息产业发展,汪玉提到了三个重要阶段: 20 世纪 80 年代后、2000 年之后以及 2010 年至今。

20 世纪 80 年代后,随着改革开放的推进,依靠人口红利和低成本优势,我国逐步建立起全球最大的电子制造基地。80 年代求学的那一批清华学子,如今已成为中国电子信息产业的中坚力量,特别是在芯片领域,他们成为产业链构建的重要推动者。2000 年,中国进入了互联网发展的变革时代,带动了基础网络设施、电子应用产品的高速发展。从 2010 年开始,中国电子信息产业进入了快速发展时期。

在汪玉看来,电子信息产业的发展有其内在规律。从技术发展的角度来看,它经历了从电子管到晶体管,再到 如今各种新型器件的演变,这是科学发展的规律使然。从产业发展的角度来看,它始终围绕着人及其活动的需求, 在基础设施和载体方面不断进行革新;基础设施从有线通信到无线通信,应用载体也从早期的电视机、冰箱等大型 家电,发展到如今的手机、平板、汽车等。汪玉指出,当前电子信息产业链基本成型,我国在工程师培养方面已具 备全球领先的能力。但如今面临的课题是,如何从并跑、追赶的状态转变为领跑。这其中的关键在于,能否培养出 更多具有创新能力和领军才能的突破性人才。

在探讨电子信息产业的未来图景时,汪玉提出了颇具洞见的观点:**数字化是推动电子信息产业发展的关键趋势,智能化是其中的重要体现**。如何让各类载体更加智能,是未来产业发展的重要方向。他认为:端侧应用将持续推进,未来的交互载体可能不再是手机、平板,而是机器人、机器狗等新型终端。人与物理世界的交互方式,还有巨大的想象空间。

#### 02 教育转型:如何培养 AI 时代的新型人才

现在,人工智能的浪潮奔涌而来,人工智能是年轻的事业,也是年轻人的事业。

人工智能的发展在一定程度上提升了人的生产能力,比如辅助编程,使编程效率大幅提高。人工智能提升了人在虚拟世界的能力,但未来一定会回到数字空间。**随着机器人领域的蓬勃发展**,随着数十亿人类与数十亿机器人共存时代的来临,其背后的组织方式值得深入思考。

而在这种变革时代,中国青年人肩负着重要使命。我国工程师培养曾长期采用标准化模式,但随着社会对人才需求的日益多元化,这种模式正急需转型。汪玉认为"对于高等教育而言,需要充分利用 AI 等技术,做到因材施教,充分挖掘学生的个人天赋和潜力,实现个性化人才培养,以适应未来 5 到 15 年的产业发展需求。"他进一步以 DeepSeeK 为例说明,AI 带来的是从硬件、软件到算法、应用的全栈式变革,学生不能再局限于单一领域,必须具备全栈思维。

这样的产业进步,就要求人才培养不应局限于传统的院系、学科划分,本科阶段应采用宽口径培养模式,研究生阶段再根据应用驱动进行专业化培养。汪玉提到,清华大学正在推动的"书院制"培养模式,正是这一理念的实践。我们也看到:截止目前,清华大学已拥有 15 个承担本科生培养任务的书院。以未央书院为例,学生在入学时不确定具体专业,而是先接受通识教育,后期再根据兴趣选择微电子、电机等不同方向。前期课程设置强调基础共通,高年级再细分专业,并与研究生培养衔接。这种模式显著扩大了学生的培养和选择空间。与传统院系的固定路径相比,书院制要求学生更主动地规划发展方向,对自主学习和自我管理能力提出更高要求,体现了"宽口径、厚基础、重交叉"的育人理念。

### 让每个学生都能发挥自身优势,而不是采用完全一样的培养模式。这是中国未来发展对人才培养提出的新要求。 03 人才培养: 研电赛是个很好的平台

谈到人才培养,谈到创新实践。在电子信息领域一直有个比较火的大赛——研电赛,1996 年由清华发起,最初只是一个小规模的竞赛。如今,它已成为覆盖 300 多所高校,数千支队伍参加的全国性赛事。大赛以面向真需求,解决真问题为出发点,全面链接产业和高校。一方面给电子信息相关领域的研究生提供高效的企业对接,增加实践历练机会,另一方面也在帮助企业寻找高校研究力量、筛选优质人才。今年换届,汪玉接任研电赛组委会秘书长。谈到研电赛,汪玉感叹到:从去年接触研电赛至今,我深切感受到,如今赛事已规模宏大,影响力深远,组织运营也十分规范。更让他欣慰的是,学生们对赛事的热情高涨,老师们也全情投入,这种氛围让他倍感振奋。

这项赛事已经走到了第 30 年,不仅见证了电子信息产业的快速发展,作为连接产业与学术的重要平台,研电 赛更是在人才培养中扮演着独特角色。谈及赛事未来发展,**汪玉介绍到,研电赛将紧密顺应产业发展趋势,在保持** 基础技术比拼的同时,将更注重通过具体载体来呈现技术应用。今年赛事将增加光载信息赛道,同时继续加大融入

## 05 芯观点 core view

人工智能、机器人等元素,既考察数字化所需的通信感知基础能力,也展现智能化技术的应用场景。希望通过赛事命题的前瞻性设计,引导学生关注未来产业发展方向。汪玉强调,研电赛不仅要激发学生的技术思考,更要鼓励他们对未来应用进行创造性想象。

在谈到研电赛的实践导向时,汪玉分析了高校与企业的互补优势。他指出,高校与企业各有所长,这种差异性恰恰构成了合作的基础。一方面,企业的生产资料,如算力、制造平台等具有明显优势,这些是高校难以企及的。更重要的是,企业面临的实际问题更贴近市场需求。另一方面,高校在科学研究和人才培养等具有明显优势,特别是在研究生培养方面,高校的科学研究始终发挥着关键作用。基于这样的定位差异,汪玉教授强调高校与企业应该加强紧密合作。同时对于合作的互补性,他进一步解释道:"企业研究通常关注 1-3 年内可实现的短期目标,而高校更适合开展 3 ~ 15 年甚至更长期的研究项目。这种时间维度的互补性,使得双方的合作能够覆盖从基础研究到应用落地的完整创新链条。"

研电赛作为互动引擎,也为高校与企业协同育人、共同发展提供了广阔空间。

#### 04 创新实践: 培养创新创业的"勇气"

汪玉不仅是一名杰出的学者,同时还是一名优秀的创业者。他和学生姚颂 2016 年创办 AI 芯片公司深鉴科技,后被赛灵思收购。2023 年,他又和博士生夏立雪创立了大模型公司无问芯穹,希望能够解决中国算力领域所面临的一些挑战和问题。

**谈及育人方向,**他一直强调宽基础,同时在夯实基础的前提下,加强与产业界的互动,使学生在 AI 学习、应用和研究过程中更具应用导向。18 岁到 27 岁这段求学时光,是一个人最宝贵的创新黄金期。在汪玉看来,"这个阶段的年轻人充满活力,敢于尝试,也不惧失败,充分激发他们的创新能力意义重大。为他们后续的深造和研究奠定基础。"

**谈到创新与创业的关系,**汪玉的观点既务实又深刻。"我们不能期望所有研究生都选择创业,创业需要具备多方面条件,创业是一件很难的事情。**重要的是培养学生的创新意识和突破的勇气。无论是在创业环境中,还是在大企业工作,都需要这种敢于创新、勇于突破的勇气。**这也是研电赛和日常教育中,需要着力培养的人才核心素养。"

当电子信息产业的浪潮奔涌向前,产教融合如同一座"桥梁":一头连着产业的现实需求,一头通向人才的未来可能;一头扎进基础研究的深水区,一头架起产学研协同的快车道。守拙砺初心,当更多年轻人带着"敢突破"的勇气走向产业前沿,中国电子信息产业的长河,必将在创新的浪潮中,奔涌向更辽阔的天地。

作者简介: 汪玉,研电赛组委会秘书长、清华大学电子工程系主任,是"育、研、创"三位一体的典范。作为 清华首位 80 后系主任和 IEEE Fellow,他不仅在智能芯片领域取得突破性成果,更成功孵化深鉴科技、无问芯穹 等业界标杆企业,推动产学研深度融合,为中国半导体产业发展贡献了清华智慧。

## 如何做好人形机器人的"五官"与"皮肤"?

当前,具身智能已成为全球技术竞逐与产业布局的核心赛道,将以不同的形态、模式、功能应用于不同的行业、领域,并逐步融入大众生活场景之中。具身智能本质是仿生学理念主导下的技术实践,而仿生技术的基础需要有大量数据支撑,来实现多参数场景刻画能力与多维度数据融合效能。人形机器人正是这一理念下的典型产品,也是 AI 技术承载与集成的平台和载体。通过多技术融合与协同和类人化设计,赋予其与环境自主交互和执行的功效。传感器作为获取环境数据信息的核心功能器件,其数据采集的

在机器人大世界展示的仿生人形机器人"小柒"

量级、维度与类型,直接决定人形机器人智能化程度或性能的优劣。犹如机器的"五官"与"皮肤",承担对环境数据的多维度感知与多数据融合功能。由此可见,搭载传感器的产品技术类型和数量成为判断与衡量机器人能效水平的标志之一。因此,未来人形机器人领域的竞争核心是感知技术(即传感器技术)。

#### 仿生技术传感器种类繁多

人形机器人中,只有大量采用不同类型的传感器技术,才能追求类人化的意识、行为、动作、功能和生物感知特征,同时具有人所不能及的独特优势和场景适应能力。

#### 视觉传感器

主要有激光、结构光、红外、热成像、可见光、立体等多种类型。激光视觉传感器测量范围通常在几十米到上百米,精度可达 ±0.01 毫米,通过发射激光束并测量反射时间创建三维模型;结构光视觉传感器图案投射精度能达 ±0.1 毫米,通过投射特定光图案分析变形获取三维信息;红外视觉可以在低光照条件下工作,感受红外光来获取图像;热成像根据物体发出的热辐射看到温度分布,常用于工业故障检测、医疗初步体温检测等;可见光感知就像人眼一样,获取彩色图像,广泛应用于安防监控、物流分拣等场景;立体视觉通过两个或多个摄像头模拟双目视差,让机器人可以感知物体的深度和距离,在机器人导航和抓取物体方面发挥重要作用。

在不同场景中的视觉传感器有不同要求。自动驾驶场景需至少 180°广视野,动态目标检测精度达厘米级;工业检测场景对分辨率要求高,能检测出微米级瑕疵。整体而言,机器人视觉在精确测距、长距离检测及微小瑕疵检测等方面远超人类,某些能力可达人眼的数十倍。

#### 听觉传感器

人形机器人中主要有以下几种类型: 首先是由多个麦克风组成阵列,可精准定位声音来源,还可降低环境噪音干扰,用于智能语音交互、会议系统等场景。从敏感材料角度来看,硅基麦克风性能稳定,压电陶瓷类具有灵敏度高,多用于各种智能终端设备;从换能原理看,常见的有动圈式和驻极体电容式;按指向性来分,有全向、单向、双向等不同类型,能满足不同场景下的声音拾取需求。在定位精度方面,高端麦克风阵列能将声音定位精度控制在±3°左右,而人耳在复杂环境中的定位精度大概在±10°~±15°。

其次是压电传感器,对声音振动非常敏感,常被用于声学检测设备、超声波等领域,其振动检测分辨率可达纳

米级,能检测到极其微小的声音振动,相比之下,人耳对这种微小振动的分辨能力要弱很多。驻极体传声器具有体积小、成本低的优点,广泛应用于手机、电脑、耳机等消费电子产品中,其灵敏度在 40dB~60dB 之间,能清晰捕捉到正常对话音量范围的声音。

#### 嗅觉传感器

金属氧化物半导体型嗅觉传感器对多种气味较为敏感,能检测出不同气体成分。在工业环境监测、空气质量检测等场景应用广泛,其成本相对较低,响应时间通常在几十毫秒到几秒,检测精度一般在 0.01~0.001 不等。而电化学型嗅觉传感器检测精度较高,可达到 ppm 级(百万分之一浓度级别),常用于医疗领域检测人体呼出气体中的特定成分,辅助诊断疾病。环游半导体红外气体传感器通过检测气体对红外光的吸收来分析气体成分,具有稳定性好、精度较高的优点,检测精度同样能达到 ppm 级,被广泛应用于化工行业的气体分析中。热释电传感器能感应气体温度变化,在一些需要实时监测气体温度的工业场景以及部分科研实验中有应用,它的响应速度相对较快,通常在几十毫秒内,但检测精度相对没那么高,在温度检测方面一般能精确到零点几度。

#### 味觉传感器

常见的有电位型和电流型。电位型基于离子电位变化实现味道识别,成本较低,在食品粗筛领域应用广泛,比如初步判断食品的酸甜属性。然而,其易受外界环境干扰,检测精度约为 10%,对味道成分解析能力有限,在不同浓度味道物质检测中易产生较大偏差。电流型检测精度较高,可达 5% 左右,响应迅速,一般在几十毫秒至数秒间,常用于食品精准调味过程控制以及水质特定味觉物质分析等对精度要求严苛的场景。

#### 触觉传感器

触觉感知场景复杂、功能繁多、技术要求高,所以其机理繁杂、种类繁多。基于材料特性分类: 一是柔性传感器。它是以导电聚合物作为敏感材料,当受到压力时,导电聚合物内部结构发生改变,进而导致电导率变化,具备良好柔韧性和较高灵敏度,检测精度可达 0.1N 左右,响应时间在 10~20 毫秒之间。常用于可穿戴电子设备、机器人皮肤等场景,能精准感知轻微的触摸和压力等。二是碳纳米管柔性传感器。它拥有出色的电学性能,在外力作用下,碳纳米管的电阻会产生变化,通过测量电阻变化可获取触觉信息。该传感器灵敏度极高,能够检测到极其微小的力,精度可达 0.01N 甚至更低。响应速度也很快,大约在 5~10 毫秒。由于制备成本高,用于高端科研设备、高精密机器人的触觉感知等方面。三是压电柔性传感器。它基于压电材料,在受到外力时会产生电荷的压电效应。响应速度极快,通常在微秒级,适合检测高频动态力,精度能达到 0.5N 左右。在医疗超声探头、智能假肢等领域应用广泛。四是离子凝胶柔性传感器。它是以离子凝胶作为敏感材料,其内部离子在受到压力时会发生迁移,从而引起电学性能改变,实现触觉感知。具有良好的柔韧性和自修复能力,检测精度在 0.2N 左右,响应时间在 15~25 毫秒。在可重构机器人、智能皮肤等前沿领域具有很大的应用潜力。

基于感知原理分类:一是电容式柔性触觉传感器。它通过检测电容变化来感知压力或触摸。结构简单,成本相对较低,检测精度大概在 1~2N 左右,响应时间在 20~30 毫秒。常用于消费电子产品的触摸按键、智能家具的交互面板等场景。二是电感式柔性触觉传感器。它利用电磁感应原理,当有物体靠近或施加压力时,会改变传感器内部的磁路,导致电感量发生变化。其具有较高的分辨率和精度,能够检测到微小位移的变化,精度可达微米级。但响应速度相对较慢,一般在几十毫秒到几百毫秒之间。在工业自动化的精密测量、机器人抓取操作等领域应用较多。

与人类触觉相比,目前的柔性多点触觉传感器虽取得一定进展,但仍存在差距。人类皮肤能感知极其微小的力度变化,分辨率极高,且能在不同温度和湿度条件下保持稳定的触觉感知能力。未来,随着材料科学、电子技术和 人工智能的持续发展,有望逐步缩小差距,使人形机器人的触觉更接近人类水平。

#### 人形机器人传感器"内""外"兼修

人形机器人中传感器涉及物理量、化学量、生物量三大敏感机理类型,以及声、力、光、磁、气、温湿度等各种类别。

从功能上看,主要可分为内传感器和外传感器。

#### 内传感器

它是机器人内部性能感知部件。

- 一是加速度传感器。当机器人在直线轨道上加速或减速运动时,加速度计能够精确测量各个方向上的加速度变化值,并同步反馈给控制系统,使机器人能够全面掌握自身的速度变化情况。陀螺仪用于测量角速度和角度,当执行转身、扭动、转弯等动作时,精准捕捉角度变化,为控制系统提供精确的姿态信息,助力其运动过程始终保持姿态平衡和稳定。

- **二是关节位置传感器。**精确测量机器人各个关节的转动角度大小值。如肩关节位置传感器可实时、精准地向控制系统反馈弯曲或伸直的具体角度数值,从而实现对机械臂等部件运动的高精度控制。

- **三是力传感器。**通常安装在关节和关键受力部件处。当执行抓取任务时,力传感器能够实时感知抓取作用力和 反作用力的大小。基于这些数据,机器人可以根据抓取物体的重量、材质等特性,精确调整抓取力度。

- **四是电流传感器。**监测控制电路中的电流、电压状况。一旦出现如过载或者即将发生短路等异常情况,控制系统及时采取应对措施,保护电路免受损害。

- **五是温湿度传感器。**监测内部关节等机械结构件、电机以及控制器电路板等关键部件的温湿度状况。长时间运行时,电路元件和机械部件在工作过程中会因摩擦产生热量,若内部温度过高或湿度过大,会引发性能退变,甚至故障。控制系统可依据数据信息和故障模型适时调整运行功率和状态,或采取相应的散热、除湿措施。

- **六是磁传感器。**根据磁场变化实现定位和导航功能。特别在特殊、复杂场景下,能够精准识别自身方位,合理 规划运动路径。

当机器人执行转身等各种复杂动作时,需要加速度计、陀螺仪、位置、力、电流、温湿度等多种内传感器技术协同和数据深度融合。控制系统基于采集到的海量数据,运用精密复杂算法,实时下达运动指令,确保机器人动作自然、流畅、安全、精准,并可提供故障范围量化数据发出警报,方便技术人员及时展开针对性的维护与调整,为长期稳定运行提供保障。

#### 外传感器

它是与外界交互的信息窗口。

如同人类"五官"和"皮肤"感知与交互外部世界信息。因此,配置多少数量和多少种类型的外传感器决定机器人的技术水平、作业能力。

根据实际功能和不同应用场景,安装不同数量的传感器,安装越多功能越强大,如视觉、听觉、嗅觉、味觉传感器一般安装 1~2 只即可实现基本功能,而触觉传感器数量因功能而异,精细操作的机器人手指等部位可能分布数十,甚至上百个。

由此可见,外传感器的类型和数量直接决定感知外部环境的能力,只有合理搭配不同类型和数量的外传感器,机器人才能更好地适应各种应用场景,实现更强大、更智能的服务功能。

#### 具身智能传感器发展潜力不可估量

具身智能传感器作为前沿科技领域的关键组成部分,正处于快速发展的关键阶段。在技术不断革新和应用场景 日益丰富的背景下,其未来发展将在敏感机理与材料、复合和模块化、产业化规模生产等多个维度展开技术创新和 市场竞争。